n-형, p-형 반도체에 관한 이야기 모음입니다.

http://idlecomputer.tistory.com/78

P형 P-type

순수한 반도체에 특정 불순물(3족 원소)을 첨가하여 정공(hole)의 수를 증가시킨 반도체.

4족 원소인 실리콘 단결정(순수 반도체)에 최외각 전자가 3개인 붕소(B) 등 3족 원소를 불순물로 첨가하면 실리콘 원자와 모두 공유 결합 후, 전가가 비어있는 상태, 즉 정공이 생긴다.

대표적인 3족 원소는

N형 N-type

순수한 반도체에 특정 불순물(5족 원소)을 첨가하여 전자(electron)의 수를 증가시킨 반도체.

4족 원소인 실리콘 단결정(순수 반도체)에 최외각 전자가 5개인 인(P), 비소(As) 등 5족 원소를 불순물로 첨가하면 실리콘 원자와 공유결합 후, 전자가 남는 상태, 즉 잉여전자가 생긴다.

PN 접합 다이오드

반도체의 이러한 성질을 이용하여 다이오드라고 하는 회로 소자를 만들어사용합니다.

P와 N을 먼저 붙힙니다.

그럼 가운데 부분에서 원자는 안정화를 원하가 때문에 P형 반도체에서 N형 반도체의 전자를 끌어 당겨 일부 정공들을 채워 안정화를 이룹니다.

이렇게 만들고 나면

이번에는 반대로 배치 하면

중간에 N형 반도체는 전지의 +정공와 결합하여 부도체가 되고 P형 반도체는 전지의 -전자와 결합하여 부도체가 됩니다.

이전의 배치보다 훨씬 많은 부분이 부도체가 되어 버립니다.

전지의 +정공에서 전지의-전자를 가져 오기위해서는 N형 반도체,P형 반도체 모두 부도체가 된상태에서 매우큰 전압을 줘야 -전자가 전지의 +정공 쪽으로 움직일수 있습니다.

그래서 아주큰 전압이 아니면 전류가 흐르지 않게 하는용도로 사용할수가 있습니다.

그리고 아주큰 전압으로 흐르게 되면 그 전압을 항복전압이라고 합니다.

너무 커서 전류를 못흐르게 하는역활을 항복 했다는 것이지요 .

다이오드의 일반적인 용도는 전류의 정류기로 사용됩니다. 그외에도 여러가지고 응용되어 사용되고 있습니다.

http://www.amkor.co.kr/archives/566

반도체 이야기, PN 접합과 다이오드

지난 번에 진성반도체, 그리고 n형과 p형 반도체의 밴드구조에 대해서 살펴보았고, 소수캐리어와 다수캐리어라는 것이 있어서 반도체의 전기전도성을 주는 것이라고 했습니다.

그럼 이 반도체에 전압을 걸어주면 어떤 일이 벌어질까요? 전기만 생각하면 머리가 아파 온다고요? 지극히 정상입니다. 왜냐하면, 전기는 눈에 보이지 않기 때문에 상상하기가 어렵지요. 이럴 때는 눈에 보이는 것으로 바꾸어 생각하는 것이 편리합니다.

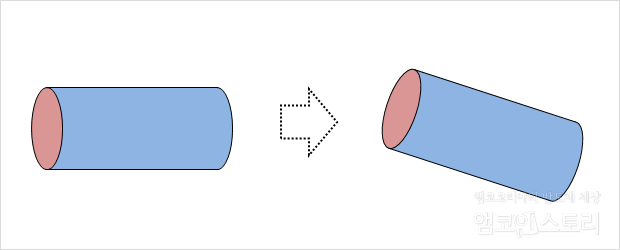

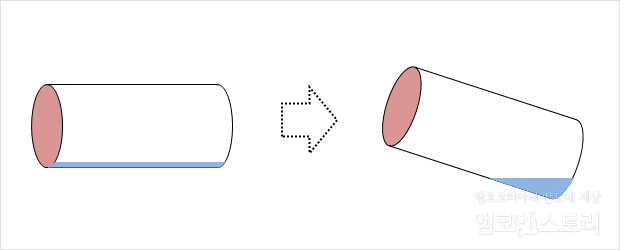

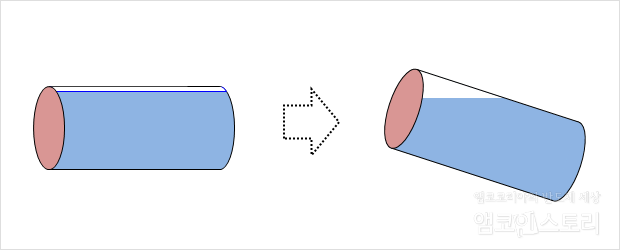

자, 용기 속에 있는 물을 떠올려 볼까요? 양쪽이 모두 막혀 있는 용기 속에 물이 꽉 찬 경우를 먼저 봅시다. 이 용기를 기울여도 물이 움직이지 않습니다. 용기의 양 끝이 막혀 있고 물이 꽉 차 있어서 움직일 수 없지요.

그럼 용기 속에 물이 약간만 차 있는 경우는 어떻게 될까요? 용기를 기울이니 물이 얕은 쪽으로 흘러가는군요. 네, 그림에서처럼 물의 이동이 있습니다.

물로 꽉 찼던 용기에 물이 일부 빠져나간 경우는 어떨까요? 용기를 기울이니 공기가 높은 쪽으로 흘러가는군요. 그렇습니다. 공기의 이동이 있지요.

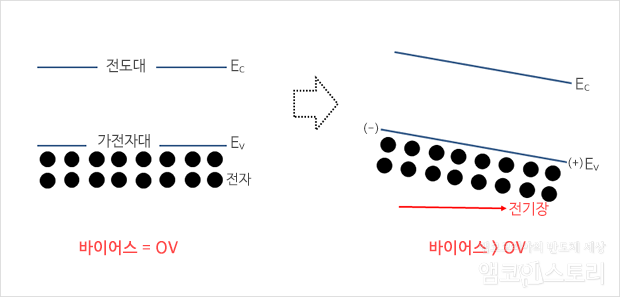

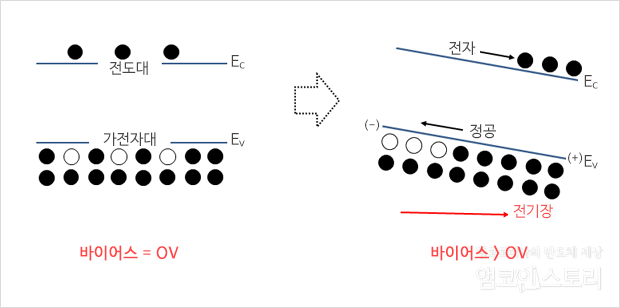

온도가 0K인 경우의 진성반도체는 모든 전자가 가전자대에 꽉 차 있어서 움직일 수 없는 상태를 말합니다. (양쪽이 막힌 용기에 물이 꽉 차 있는 경우와 같으며, 물은 전자로 생각하면 되겠습니다) 이 경우에 전압을 걸어 주면 (용기를 기울이는 것과 같습니다) 밴드가 기울어집니다. 높은 쪽이 ‘-‘이고 낮은 쪽이 ‘+ ’입니다. 이때에는 모든 전자가 가전자대에 꽉 차 있기 때문에, 밴드가 기울어져도 움직일 수 있는 전자는 없습니다. ‘전자가 움직이지 않는다’는 것은 ‘전류가 흐르지 않는다’는 것을 말합니다.

온도가 0K보다 높아서 가전자대의 일부 전자들이 열에너지를 받아 전도대로 올라갔습니다. 물론 가전자대에 정공(전자의 빈자리)이 동시에 생성되었지요. 전도대의 전자는 위의 ‘용기 속의 물’ 모델에서 용기 속에 물이 약간만 차 있는 경우로 생각해볼 수 있습니다. 전압이 걸리면 ‘+ ’ 쪽으로 모이게 됩니다. 가전자대에 생성된 정공은 ‘용기 속의 물’ 모델에서 물이 일부 빠져나간 용기 속의 빈 공간(공기)으로 생각하면 되는데, 전압이 걸리면 ‘–‘ 쪽으로 모이게 됩니다. 전자와 정공이 서로 반대 방향으로 움직였네요, 전류가 흐른다는 뜻입니다. 쉽지요?

진성반도체를 먼저 설명한 이유는, 캐리어에 대한 이해를 높이기 위함이었습니다. 온도가 0K보다 높을 때, 전도대로 뛰어 올라간 전자와 가전자대에 남겨진 정공의 쌍이 생성되는데, 이들을 캐리어라고 부릅니다. ‘용기 속의 물’ 모델에서는 물과 공기가 캐리어가 되겠지요. 이들 캐리어는 전압을 걸어주면 움직입니다. (전도대의 전자와 가전자대의 정공이 움직이는 것입니다)

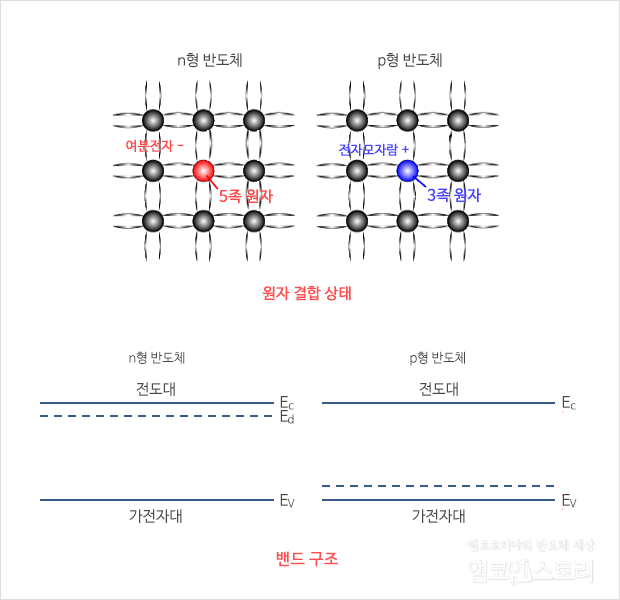

이제 p형과 n형의 반도체를 생각해 보도록 합시다. 최외각전자가 5개라서(5족 원자) 4개의 전자가 공유결합을 이루고, 하나의 전자가 여분으로 남아있는 n형 반도체와, 최외각전자가 3개라서(3족 원자) 4개의 공유결합을 충족하는데 전자가 하나 모자란 상태인 p형 반도체가 있습니다. 온도가 0K일 때는 모든 전자가 핵에 붙들려 있어서 움직일 수 있는 전자(또는 정공), 즉 캐리어가 없습니다. 밴드 구조에서 5족 원자(또는 3족 원자)는 에너지갭 내에 도너 레벨(또는 억셉터 레벨)을 전도대(또는 가전자대) 근처에 형성하고 있지만, 아직 이들을 이온화하고 전도대로 뛰어 올라간 전자나 가전자대에 생성된 정공이 없는 상태입니다.

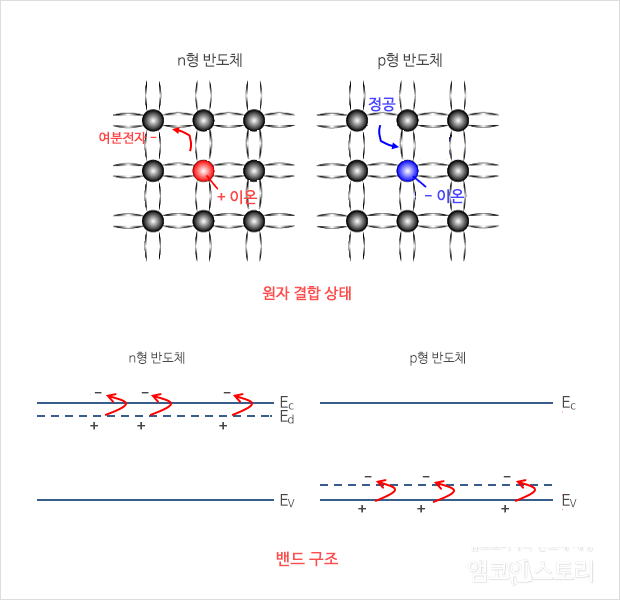

온도가 실온(대략 298K)이면 대부분 불순물원자(도너 또는 억셉터)들이 이온화되면서 여분의 전자를 전도대에 올리거나(n형 반도체), 가전자대에 정공을 형성합니다(p형 반도체). 여분의 전자를 잃은 도너(n형 반도체)는 양이온(음의 전기를 갖는 전자를 잃었으므로 양의 전기를 띠게 되지요)으로, 주변의 실리콘 원자로부터 전자를 받아서 4개의 공유결합을 이루게 된 억셉터(p형 반도체)는 음이온(음의 전기를 갖는 전자를 하나 받았으므로 음의 전기를 띠게 되지요)으로 변합니다.

움직일 수 있는 캐리어는 전도대에 있는 전자와 가전자대에 있는 정공이라고 했습니다. 전도대에 전자가 올라가 있는 n형 반도체의 다수캐리어는 전자이고, 가전자대에 정공이 형성되어 있는 p형 반도체의 다수캐리어는 정공입니다. 캐리어를 형성하고 뒤에 남은 이온(n형 반도체에서는 양이온, p형 반도체에서는 음이온이지요)들은 공유결합으로 묶여 있어서 움직이지 못하므로 캐리어가 될 수는 없음에 유의하세요! (나중에 캐리어들의 움직임을 설명할 때 혼동될 수 있습니다)

이와 같은 n형과 p형의 두 반도체를 붙이면 어떤 일이 벌어질까요? 이것을 pn접합(P-N접합, PN접합)이라고 부르며, 여기서부터 반도체의 수많은 기능이 탄생하게 되었답니다. 이 pn접합은 반도체 디바이스를 이해하는 기본이므로 가장 중요한 부분입니다. 다소 복잡한 내용이므로 정신 똑바로 차려야겠습니다.

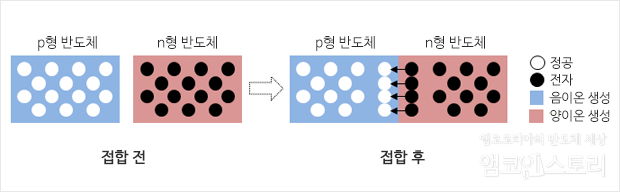

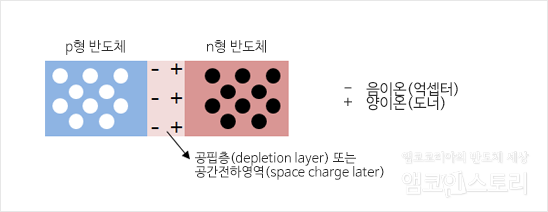

정공이 다수캐리어인 p형 반도체(흰 점으로 표시된 것이 정공입니다)와 전자가 다수캐리어인 n형 반도체(검정 점으로 표시된 것이 전자입니다)가 한 면에서 만났습니다. 만나기 전에는 각각의 다수캐리어들은 균일하게 분포하여 있었습니다. 물론 이온화된 도너 또는 억셉터도 균일하게 분포하여 있으며, 각각의 반도체는 전기적으로 중성인 상태입니다. (p형 반도체에서는 음이온과 정공의 수가 같고, n형 반도체에서는 양이온과 전자의 수가 같으므로 전기적으로는 중성입니다) 그러다가 한 면에서 두 반도체가 만나면 접합면 부근의 정공(p형 반도체의 다수캐리어)과 전자(n형 반도체의 다수캐리어)가 서로 끌려 오다가 만나겠지요. (이때, 이온화된 도너나 억셉터는 움직이지 않고 고정되어 있음에 유의하세요)

정공과 전자가 만나면 어떻게 될까요? 그냥 없어집니다. (정공은 전자의 빈자리이므로 전자를 만나면 빈자리가 채워지는 셈이므로 아무것도 남지 않겠지요) 이것을 전자와 정공의 재결합이라고 부릅니다. 전자와 정공의 재결합이 일어나면 재미있는 현상이 벌어지게 됩니다. 차근차근 이해해 보도록 합시다.

전자와 정공은 혼자서 저절로 생겨난 것이 아니라, 반드시 그 자리에 양이온과 음이온을 생성한다고 했지요. (n형 반도체는 도너를 이온화시키면서 전자가 전도대로 올라가는 것임을 기억하세요, p형 반도체는 억셉터를 이온화시키면서 정공이 가전자대에 생성되는 것이고요) 전자와 정공이 재결합한 자리에는 음이온(p형 반도체)과 양이온(n형 반도체)만 남게 됩니다.

접합이 이루어지기 전에는 각 반도체 내에는 다수캐리어와 불순물(도너 또는 억셉터) 이온이 같은 수로 있어 전기적으로 중성이었는데, 접합이 이루어진 후에는 접합면 부근 다수캐리어들이 재결합을 이루며 소멸하여, 그 부분에는 이온들만 존재하게 되므로 전기적 중성이 깨지게 됩니다. 이렇게 다수캐리어들이 재결합으로 소멸한 접합면 부근의 영역을 공핍층(depletion layer, 다수캐리어가 없어졌으므로)이라고 부르고, 결과적으로 전기적 중성이 깨져서 전하를 띠게 되므로 공간전하영역(space charge layer)이라고도 부릅니다.

각각의 반도체 영역에서 다수캐리어들이 모두 접합면으로 끌려와 재결합하면서 소멸해버리면 전류가 흐를 수 없는 부도체가 되어버리겠다는 걱정이 안 드나요? 걱정하지 마세요. 다행스럽게도 pn접합을 하면서 생성된 공핍층이 그런 일이 일어나지 않도록 막는 장치니까요. 전자와 정공이 재결합하면서 소멸(공핍층이 생기고)하고 이온(p형 반도체 쪽에는 음이온, n형 반도체 쪽에는 양이온)들만 남아서 p형 반도체 쪽에 ‘–‘ 전기를, n형 반도체 쪽에는 ‘+ ’ 전기를 띠게 되므로 공핍층 내에 전위(potential)가 형성됩니다.

이 전위는 n형 반도체 내의 전자가 p형 반도체 쪽으로 접근하는 것을 막아 평형을 이루게 됩니다. (p형 반도체 쪽에 생겨난 ‘–‘ 전기가 전자의 접근을 막지요) 마찬가지로, p형 반도체 내에 있던 정공들도 이 전위로 인해 더 n형 반도체 쪽으로 접근할 수 없게 됩니다. (n형 반도체 쪽에 생겨난 ‘+’ 전기가 정공이 접근하지 못하도록 밀어내지요) 이렇게 공핍층 내 이온으로 인해 생겨난 전위로 다수캐리어들이 더 끌려올 수 없도록 전위장벽이 생기는데, 이를 접촉전위(contact potential)라고 부르며 실리콘 pn접합일 때 접촉전위의 크기는 대략 0.6~0.7V 정도 됩니다.

이렇게 p형 반도체와 n형 반도체를 한 면에 접촉해 놓은 것이 반도체 소자의 가장 기본인 다이오드입니다. 축하합니다! 기본적인 반도체 물리학을 이해하게 되었고, 드디어 반도체 소자로 넘어가도록 하겠습니다.

위의 다이오드에 전압을 걸어주면 어떻게 될지 살펴봅시다. 먼저 전압을 걸어주기 전을 생각해 봅시다. 물이 담긴 대야의 한 부분에 잉크를 한 방울 떨어뜨리면 어떻게 될까요? 잉크는 떨어진 지점으로부터 번져나가 결국 대야 전체에 균일하게 섞이게 될 테지요. 이것을 확산이라고 부릅니다. 농도가 높은 곳으로부터 낮은 곳으로 물질이 이동하여 결국 농도의 차이가 없도록 균일하게 섞이게 되는 것이지요.

그럼, 위의 p형 반도체와 n형 반도체에서는 확산 현상에 대해서 어떻게 생각해야 할까요? 즉, 전압을 걸어주지 않아도 확산으로 정공이 많은 p형 반도체 쪽에서 n형 반도체 쪽으로 이동함으로써 (전자가 많은 n형 반도체 쪽에서 p형 반도체 쪽으로 이동함으로써) 전류가 흘러야 하지 않을까요? 정답은 “No!”입니다.

물론 처음에는 각 다수캐리어의 농도 차이로 확산이 일어나 전자와 정공의 재결합이 일어나지요. 그러면서 공핍층이 생겨나고 전위장벽(접촉전위)이 발생해 그 이상의 확산을 막습니다. 즉, 농 차로 인해 각 다수캐리어들이 확산하려고 하는 경향과 전위장벽이 평형(줄다리기를 생각해 봅시다. 힘의 크기가 같아서 이쪽으로도 저쪽으로도 움직이지 못하는 상태를 ‘평형상태’라고 말하지요)을 이루어 캐리어들이 움직이지 못합니다. 즉, 다이오드에 전압을 걸어주기 전에는 전류가 흐르지 않습니다.

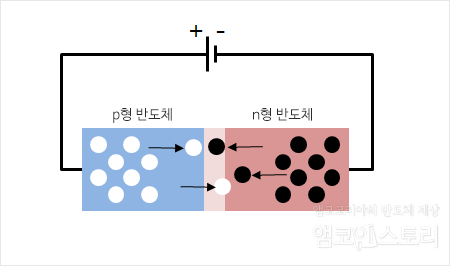

이제 다이오드에 전압을 걸어주는 경우를 두 가지로 나누어 생각해 봅시다. 먼저, p형 반도체 쪽에 ‘+’ 단자를, n형 반도체 쪽에 ‘–‘ 단자를 연결하게 되면 이것을 순방향 바이어스(forward bias)를 걸어준다고 표현합니다.

정공과 전자가 신이 났습니다. 전위장벽 때문에 꼼짝 못 하고 있다가 순방향으로 전압을 걸어주면(순방향 바이어스) p형 반도체 내에 있던 정공들은 접합면을 넘어 ‘–‘ 전압이 걸려있는 n형 반도체 쪽으로 달려가고 n형 반도체 내에 있던 전자들은 접합면을 넘어 ‘+’ 전압이 걸려있는 p형 반도체 쪽으로 달려갑니다. 접합면을 지나 n형 반도체 쪽으로 들어간 정공은 소수캐리어(n형 반도체의 다수캐리어는 전자이므로 정공은 소수캐리어가 되는 것을 상기하세요)가 되고, 접합면을 지나 p형 반도체 쪽으로 들어간 전자 역시 소수캐리어(p형 반도체의 다수캐리어는 정공이므로 전자는 소수캐리어가 되겠지요)가 되어 전류를 흐르게 합니다. 이 전류를 소수캐리어에 의한 전류라고 부릅니다.

다이오드에 흐르는 전류는 소수캐리어로 작용하는 정공과 전자에 의한 전류의 합이 됩니다. 외부에서 전압이 계속 유지되는 동안은 전원으로부터 캐리어들이 계속 공급되는 셈이므로, 위의 현상이 계속 일어나게 되겠지요. 한 가지 더 생각해 본다면, 걸어주는 전압은 최소한 전위장벽보다는 커야 다수캐리어들이 전위장벽을 넘어 상대편 반도체 쪽으로 넘어갈 것입니다.

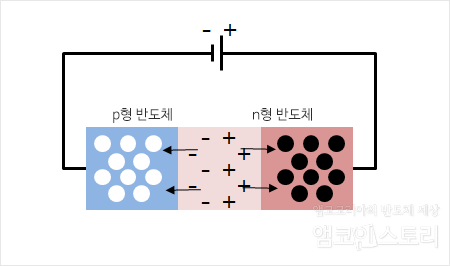

이제, p형 반도체 쪽에 ‘-‘ 단자를, n형 반도체 쪽에 ‘+’ 단자를 연결하는 경우를 생각해봅시다. 이것은 역방향 바이어스(reverse bias)를 걸어준다고 표현합니다. 전자는 ‘+’ 단자 쪽으로 끌리고, 정공은 ‘–‘ 단자 쪽으로 끌리게 되는데, ‘+’ 단자는 n형 반도체 쪽에, ‘-‘ 단자는 p형 반도체 쪽에 연결되어 있으므로 전자는 n형 반도체 쪽으로, 정공은 p형 반도체 쪽으로 끌리게 되는 셈입니다.

즉, 각 반도체의 다수캐리어들이 접합면으로부터 더 멀어지게 됩니다. 다수캐리어가 접합면으로부터 멀어지면, 그 영역에는 도너 또는 억셉터의 이온만 남게 되므로 결국 공핍층이 더 커지고 (공간전하영역이 확대되겠지요) 전위장벽은 더 높아지게 됩니다. 즉, 다수캐리어는 접합면을 넘어 상대편 반도체 쪽으로 넘어가지 못하므로 다수캐리어에 의한 전류는 흐르지 못합니다.

그러나 소수캐리어에 의한 전류를 고려해야 합니다. p형 반도체 내부에는 적은 양의 전자(소수캐리어)가 존재하고 n형 반도체 내부에도 적은 양의 정공(소수캐리어)이 존재합니다. 이들은 도너와 억셉터에 의해서 생겨난 것이 아니라 실리콘 자체에서 발생한 것들인데 (진성반도체의 경우 상온에서 실리콘 내의 일부 전자가 열에너지를 얻어 전도대로 올라가면서 가전자대에 정공을 남긴다는 것을 기억하세요) 상온에서 이들의 양은 극히 적습니다. P형 반도체 내에 있는 전자(소수캐리어)는 역방향 바이어스에 의해 p형 반도체 쪽으로부터 n형 반도체 쪽으로 접합면을 통과하여 흐르고 n형 반도체 내에 있는 소수캐리어로서의 정공 역시, n형 반도체 쪽으로부터 p형 반도체 쪽으로 접합면을 통과하여 흐르므로 소수캐리어에 의한 전류가 흐르게 되는데, 이 전류를 역포화전류(reverse saturation current)라고 부릅니다.

소수캐리어의 양이 극히 적으므로 역포화전류는 무시할 수 있습니다. 결론적으로 순방향 바이어스를 걸어주면 다이오드에 전류가 흐르고, 역방향 바이어스를 걸어주면 다이오드에 전류가 흐르지 않는 것으로 이해하면 됩니다.

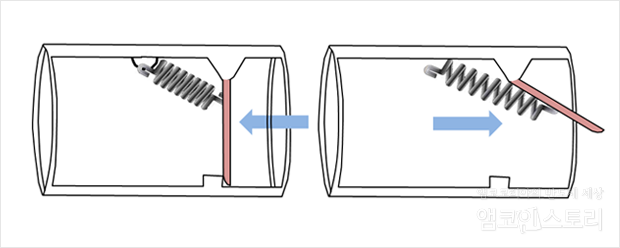

다이오드의 전기적 특성은 물의 흐름으로 생각하면 쉽겠네요. 물이 한 방향으로는 흐를 수 있고 반대 방향으로는 흐를 수 없도록 만들어진 특수한 파이프를 생각해봅시다. 파이프 내부에는 물의 흐름을 제어할 수 있는 판이 장치되어 있는데, 이 판은 앞 뒤로 움직일 수 있게 되어있으며 스프링에 연결되어있습니다.

파이프의 아래쪽 벽에는 스토퍼가 장치되어 있어서 판이 한쪽으로는 열릴 수 있지만 반대쪽으로는 열릴 수 없도록 했습니다. 물이 흐르지 않을 때는 스프링에 의해 판이 잡아 당겨져 파이프가 막히게 됩니다. 물을 오른쪽에서 왼쪽으로 흐르게 해볼까요? 수압이 왼쪽으로 걸리지만 판이 스토퍼에 걸려서 파이프가 여전히 막혀 있으므로, 물이 흐를 수 없습니다.

그럼 반대 방향으로 물을 흐르게 해 볼까요? 반대 방향으로 수압이 걸리면, 판이 열리면서 (스프링이 늘어났군요) 물이 왼쪽에서 오른쪽으로 흐르게 됩니다. 여기서 한 가지 알아야 할 것이 있습니다. 수압이 스프링의 힘보다 커야 판이 열리고, 작으면 판이 열리지 않으므로 물이 흐를 수 없다는 것입니다. 수압은 걸어준 전압으로, 수압의 방향은 바이어스의 방향으로, 물의 흐름은 전류로, 스프링의 힘을 전위장벽으로 이해하면 되겠네요!

http://www.amkor.co.kr/archives/564

PNP접합과 바이폴라 접합트랜지스터(BJT)

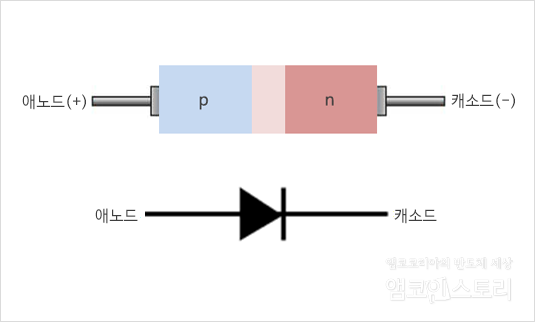

지난 번에 p형 반도체와 n형 반도체를 한 면에서 접촉해 다이오드(pn 접합다이오드)를 만들어 보았습니다. 생각보다 복잡하고 이해하기 까다로웠을 것입니다. 다시 한 번 정리하자면, p형 반도체 쪽에 전압이, n형 반도체 쪽에 –전압이 걸리면 순방향 바이어스가 되어 전류가 흐르지만, 반대로 전압이 걸리면 역방향 바이어스가 되어 전류가 흐르지 않는데, 이를 설명하기 위해 각 반도체 영역의 다수 캐리어와 소수 캐리어의 거동에 대해 지난 번에 설명했습니다. 이러한 pn 접합다이오드의 대략적인 모식도와 기호는 아래 그림과 같습니다.

▲ pn 접합다이오드 ⓒ백종식

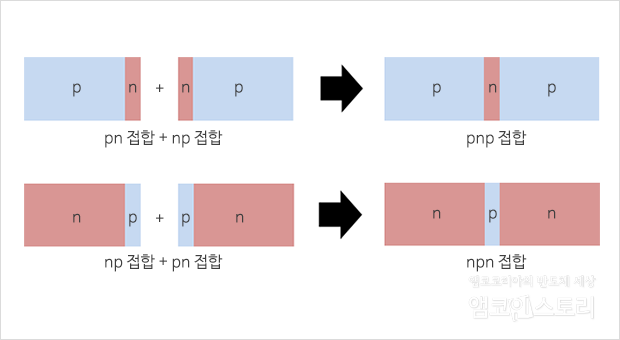

이번에는 한 발 더 나가서, 그렇게 만들어진 다이오드 2개를 붙여 pnp(또는 npn) 접합트랜지스터를 만들어 보려고 합니다. 지난 번의 내용이 아직도 이해가 되지 않았다면 다시 돌아가 정독해 주세요. 이 내용을 이해하기 위해서 꼭 필요하답니다.

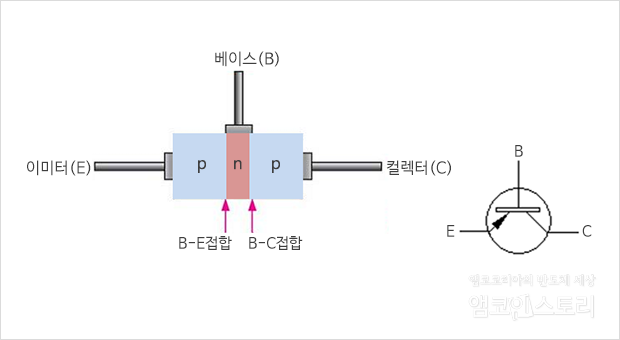

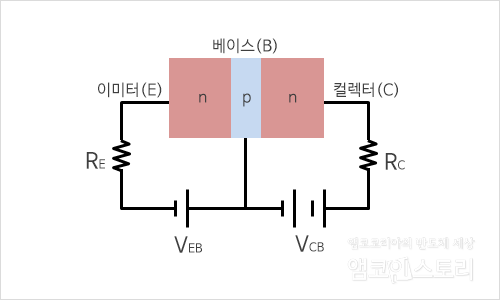

pnp 접합트랜지스터의 대략적인 모식도와 기호는 아래 그림과 같습니다. 접합다이오드에서와는 달리 반도체 영역이 3개 있습니다. 이미터, 베이스, 그리고 컬렉터입니다. (혹시 위의 다이오드 모식도와 아래 트랜지스터의 모식도가 똑같이 세 개의 영역으로 나누어져 있다고 혼동하는 독자가 있을지도 모르겠네요. 위의 다이오드 모식도에서 가운데 있는 영역은 공핍층을 나타낸 것이고, 아래의 트랜지스터 모식도에서 가운데 있는 영역은 반도체입니다. 엄밀히 그리자면 아래의 트랜지스터 모식도에서 B-E접합면과 B-C접합면에 공핍층이 있어야 합니다만, 트랜지스터에서는 모식도를 단순하게 나타내기 위해 공핍층을 그려 넣지 않았으니 혼동하지 마세요!)

▲ pnp 접합트랜지스터 ⓒ백종식

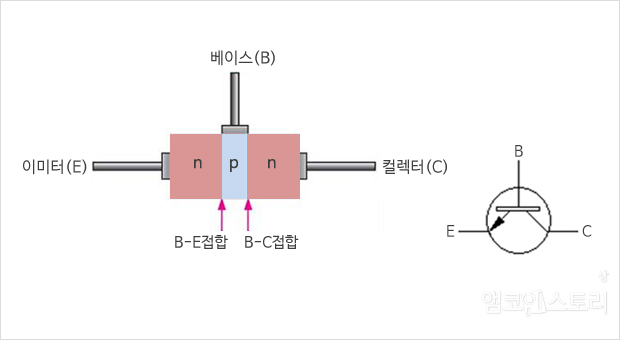

npn 접합트랜지스터의 모식도와 기호는 아래와 같습니다. 기호를 보면 이미터의 화살표가 반대로 되어있는 것만 다르고 똑같이 생겼네요.

▲ npn 접합트랜지스터 ⓒ백종식

자, 그럼 이러한 접합트랜지스터가 어떻게 작동하게 되는지 간단히 살펴볼까요? npn 접합트랜지스터와 pnp 접합트랜지스터의 작동방식은 비슷하므로 npn 접합트랜지스터의 작동방식만 살펴보기로 하겠습니다. 이미터 쪽에 순방향 bias를 걸어주고 (이미터의 n 쪽에 음의 전압을 베이스의 p 쪽에 양의 전압을 걸어주는 것) 컬렉터 쪽에 역방향 bias를 걸어주면 (컬렉터의 n 쪽에 양의 전압을, 베이스의 p 쪽에 음의 전압을 걸어주는 것) 작동하게 됩니다.

이해가 잘 안 된다고요? 그럼 하나씩 뜯어서 살펴봅시다. 이미터와 베이스 사이에 순방향 bias를 걸어주면 이미터에서 베이스 쪽으로 전자(이미터 반도체 내의 다수 캐리어)가 주입되고 베이스에서 이미터 쪽으로 정공(베이스 반도체 내의 다수 캐리어)이 주입됩니다. 한 가지 중요한 점은, 일반적으로 이미터 쪽의 불순물 도핑 양이 베이스 쪽의 불순물 도핑 양보다 훨씬 많으므로 이미터에서 베이스 쪽으로 주입되는 전자의 양이 베이스에서 이미터 쪽으로 주입되는 정공의 양보다 훨씬 많음에 유의하세요.

전자와 정공이 만나면 재결합하게 되는데, 전자의 양이 정공의 양보다 훨씬 많아서 대부분의 전자는 재결합하지 않은 채 컬렉터 쪽으로 넘어가 컬렉터 전류를 이룹니다. 베이스 반도체 영역은 일반적으로 작게 만듭니다. 그 이유는, 전자와 정공의 재결합 가능성을 낮추어 더 많은 수의 전자가 이미터에서 컬렉터 쪽으로 살아서 갈 수 있도록 해주기 위함입니다.

이제 컬렉터와 베이스 간의 bias를 살펴볼까요? 컬렉터와 베이스간에 역방향 bias를 걸어주면(컬렉터의 n 쪽에 양의 전압을, 베이스의 p 쪽에 음의 전압을 걸어주는 것을 말합니다) 베이스 영역을 살아서 통과한 전자가 양의 전압에 의해 이끌려 컬렉터 영역을 무사히 통과하게 되어 컬렉터 전류를 이루게 됩니다.

▲ pnp 접합 ⓒ백종식

이번에는 다른 시각으로 한 번 살펴보겠습니다.

일반적으로 이미터 쪽의 도핑은 컬렉터에 비해 높습니다. 베이스 영역을 빼고 생각해 본다면 이미터에서 컬렉터 쪽으로 전자 농도의 차이가 있으므로 전자의 흐름이 있어서 전류가 흘러야 합니다. 하지만 가운데 베이스가 끼어 전위장벽을 형성하므로 전자가 이동할 수 없어서 평상시에는 전류의 흐름이 없습니다. 베이스의 전위장벽을 낮춰주면 비로소 이미터에서 컬렉터 쪽으로 흐르게 되겠군요. 전위장벽이 낮아질수록 전자의 흐름이 더 수월해지겠네요.

즉, 이미터에서 컬렉터 쪽으로 흐르는 전자의 양, 다른 의미로 컬렉터에서 이미터 쪽으로 흐르는 전류의 양이 베이스 영역의 전위장벽에 의해서 조절됩니다. 베이스 영역의 전위장벽은 베이스 전류에 의해서 조절됩니다. 결론적으로, 컬렉터에서 이미터로 흐르는 전류의 양은 베이스 전류에 의해서 조절된다고 할 수 있겠습니다. 그런데, 베이스 전류는 일반적으로 매우 낮습니다.

다시 말해, ‘매우 낮은 베이스 전류를 가지고 컬렉터와 이미터 간의 전류를 조절한다’는 것인데, 다른 시각으로 보면 ‘베이스 전류의 작은 변화가 컬렉터와 이미터 간의 전류를 크게 변화시킨다’는 것으로 이해할 수 있습니다. 이것을 우리는 전류증폭이라고 부릅니다. (베이스 전류의 작은 변화를 입력으로 주면 컬렉터와 이미터 간의 큰 전류 변화가 출력으로 나타난다는 것이지요) 이것을 접합트랜지스터의 활성모드라고 부릅니다.

▲ npn BJT의 작동원리 ⓒ백종식

역시, 전자나 전류의 흐름은 눈에 보이는 것이 아니라서 이해가 잘 안 되기 마련이지요. 물의 흐름으로 생각해 보면 이해가 훨씬 쉬울 것 같습니다.

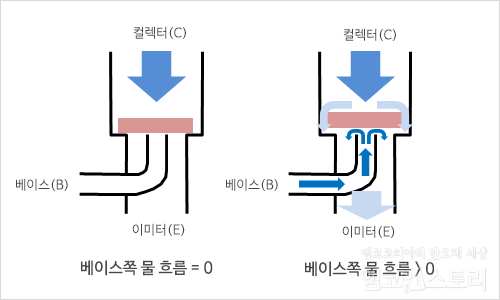

아래 그림과 같은 특수한 파이프를 생각해봅시다. 파이프의 입구 부분을 컬렉터, 출구 부분을 이미터로 생각하겠습니다. 이미터 쪽의 측면에 가느다란 파이프가 관통해 들어와 있는데, 입구 쪽은 베이스로 연결되어 있고, 출구 쪽은 컬렉터와 이미터 사이에 있는 밸브와 맞닿아 있습니다. 컬렉터 쪽에는 물이 항상 틀어져 있어 밸브만 열리면 컬렉터에서 이미터 쪽으로 물이 흐를 수 있으나, 평상시에는 밸브가 닫혀 있어 이미터 쪽으로 물이 흘러갈 수 없습니다. 그리고 이 밸브는 스프링이 달려서 일정 이상의 힘이 가해져야 열리도록 제작되어있습니다.

아래의 왼쪽 그림을 볼까요? 평상시 모습으로 밸브가 닫혀 있어서 컬렉터와 이미터 사이에 물이 흐르지 않습니다. 자, 이제 베이스 쪽에 물을 약간씩 흘려보내겠습니다. 밸브에 연결된 스프링을 이길 수 있는 만큼의 수압이 걸리자 밸브가 약간 열립니다. 순간, 베이스에서 이미터 쪽으로 약간의 물이 흐르고, 컬렉터에서 이미터 쪽으로도 물이 흐르기 시작합니다.

베이스 쪽의 물의 양을 더 늘리자 밸브가 더 많이 열리고, 컬렉터에서 이미터 쪽으로 흐르는 물의 양이 훨씬 많아집니다. 당연히 베이스에서 이미터 쪽으로 흐르는 물의 양도 증가하겠지요. 하지만 베이스에서 이미터 쪽으로 흐르는 물의 양은 매우 적어서 (파이프의 직경이 매우 작아서) 이미터 쪽으로 흐르는 물 대부분은 컬렉터에게서 온 것입니다.

정리해 보겠습니다. 베이스 쪽에서 공급해 주는 물의 양은 적지만, 그 양에 따라서 밸브의 열리는 정도가 달라지고, 그에 따라서 컬렉터로부터 이미터로 흐르는 물의 양이 조절됩니다. 이미터로 나오는 물의 양은 컬렉터에서 흘러온 물의 양과 베이스로부터 흘러온 물의 양의 합과 같습니다.

▲ npn BJT의 작동원리, 사진 출처 : http://goo.gl/7uhBem

바이폴라 접합트랜지스터(BJT)의 모드는 활성모드 이외에도 차단모드와 포화모드가 있으며 이는 각 단자에 전압을 어떻게 걸어주느냐에 따라서 결정이 됩니다만, 여기에서는 활성모드만 간단히 설명하는 것으로 마무리하도록 하겠습니다.

여기서 잠깐! BJT의 뜻만 간단히 살펴보고 다음으로 넘어가겠습니다.

Bipolar (n과 p 두 개의 극성을 가지고 있으며 전자와 정공 두 다른 캐리어가 전류 흐름에 관여합니다) Junction (pn접합과 np접합 두 다른 접합이 합쳐져 있습니다) Transistor

트랜지스터는 트랜스와 레지스터의 합성어로써, 트랜스는 ‘변화시키다’라는 의미가 있고, 레지스터는 ‘저항’이라는 의미가 있습니다. 트랜지스터는 저항의 값을 변화시키는 소자라고 이해하면 됩니다. 옴의 법칙(Ohm’s law)에서는 전압=저항X전류의 관계가 있으므로 저항의 값을 변화시킨다는 것은 전류의 값을 변화시키는 것으로도 해석할 수 있겠군요. 즉, 트랜지스터의 의미(전류의 값을 변화시킬 수 있다)와 목적(입력전류의 변화로 출력전류를 변화시킨다. 다른 말로는 작은 입력 전류의 변화가 큰 출력 전류의 변화를 일으키는 전류증폭을 이룬다)이 맞아 떨어지는 셈입니다.

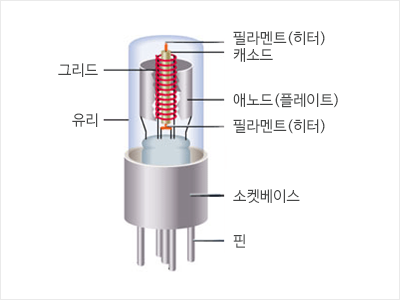

바이폴라 접합트랜지스터와 비슷한 기능을 하던 3극 진공관을 한 번 살펴보도록 하지요.

▲ 3극 진공관의 구조, 사진 출처 : http://goo.gl/d2yFo3

3극 진공관의 내부에는 양의 전압을 걸어줄 수 있는 애노드(anode), 음의 전압을 걸어줄 수 있는 캐소드(cathode), 그리고 전류의 흐름을 제어하는 그리드(gride)가 기본적으로 설치되어 있습니다. 여기에 열전자를 생성하는 필라멘트(filament)가 캐소드 쪽에 더해 있습니다. 필라멘트 전극에 전원을 연결하면 텅스텐 필라멘트가 가열되어 열전자가 튀어나오고, 애노드와 캐소드에 전압이 인가된 경우에 열전자는 캐소드에서 애노드 쪽으로 가속되어 이동합니다.

그런데, 캐소드와 애노드의 사이에 있는 그리드에 양의 전압이 걸리면 애노드 쪽으로 열전자가 이동해 전류를 발생시키지만, 반대로 그리드에 음의 전압이 걸리면 반발력에 의해 열전자가 이동하지 못해 애노드로의 흐름이 중지되고 전류가 흐르지 않게 됩니다. 이렇게 그리드의 전압을 가지고 애노드로부터 캐소드까지의 전류의 흐름(캐소드로부터 애노드까지의 전자의 흐름)을 제어하는 3극 진공관은 그 기능이 BJT를 닮았습니다. 아니 사실은 BJT가 3극 진공관의 기능을 닮도록 발명된 것이 맞는 말입니다.

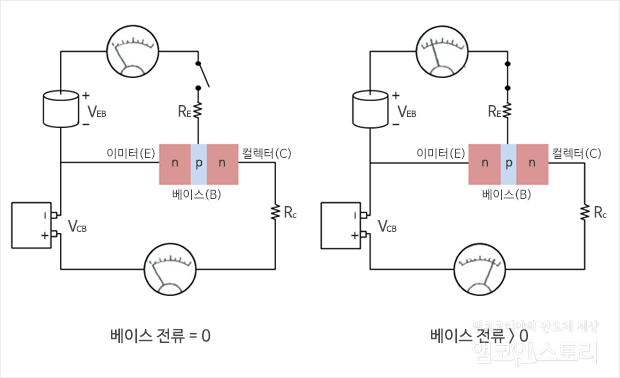

마지막으로 npn BJT의 회로를 살펴보고 트랜지스터의 증폭되는 현상을 설명하면서 이번 호를 마무리하고자 합니다.

왼쪽 그림은 스위치가 열려 있어서 베이스 전류가 흐르지 않는 상태를 나타내고 있고, 오른쪽 그림은 스위치가 닫혀 있어서 베이스 전류가 흐르는 상태로 트랜지스터가 작동하는 것을 보여줍니다. 이미터와 컬렉터 사이에는 상당한 부하의 일을 하기 위해 큰 전원(사각형 모양의 전원으로 표시하였습니다)이 설치되어 있고, 이미터와 베이스 사이에는 트랜지스터의 스위치 역할을 하기 위한 작은 전원(원통형 건전지 형태로 표시하였습니다)이 설치되어 있습니다. 스위치가 열려 있는 경우에는 전류계의 바늘이 둘 다 ‘0’을 가리키고 있네요. 스위치가 닫혀 있는 경우에는 이미터와 베이스 사이에 있는 전류계의 바늘이 약간 움직인 것으로 나타나며, 이미터와 컬렉터 사이에 있는 전류계의 바늘은 많이 움직인 것으로 나타납니다.

결론적으로, BJT는 작은 전류를 가지고 큰 전류의 흐름을 조절하는 기능을 갖습니다. 전류증폭이라는 의미는 ‘작은 입력전류의 변화를 통해 큰 전류의 변화를 출력할 수 있다’는 의미입니다. 실제로 응용할 때는 작은 신호를 큰 신호로 증폭하는 데 사용합니다.

▲ Npn BJT 회로 ⓒ백종식

이번에는 pn접합 두 개를 이어 붙여서 pnp 또는 npn의 BJT를 형성하는 것과 작동원리(전류증폭)에 대해 살펴보았습니다.

‘반도체’에 관한 나무위키의 내용 – 2018년 9월 30일 현재

1. 개요

半導體

전자공학의 눈부신 발전을 이끈 핵심 재료.

일반적으로 전기적으로 도체와 부도체 사이의 성질을 띠고 있는 물질이라고 하나, 정확한 정의를 위해서는 에너지 띠(Energy Band) 와 금지대역또는 띠틈(Forbidden Zone/Band Gap)등 양자역학적 개념이 필요하다. 대표적으로 탄소–규소–저마늄[1]으로 이어지는 14족의 물질들이 이에 해당하며, GaAs와 같이 13-15족 등 14족을 가운데로 하는 두 물질의 화합물도 이 성질을 갖는 경우가 있다.

보통 경제 기업, 산업 등에서 이야기 할 때의 반도체는 물질 그 자체보다 반도체 소자(Semiconductor Device)를 이야기하는 경우가 많다. 이 분야는 반도체 물질을 이용해서 전기회로의 가장 기본적인 요소를 만들어내는 것이다. 상세한 것은 후술

2. 에너지띠 이론

에너지띠란 윈자군 전체에 걸리는 전자의 이동범위 또는분자전체에 걸리는 에너지 준위를 모두 겹치고 싸여 만들어 지는 것이다. 따라서 물리학 에서 말하는 에너지 의 원자 하나가 아니라 다원자이다.

에너지띠 이론은 크게 두 가지로 설명할 수 있다. 하나는 준자유전자모델(Nearly Free Electron model)이고, 다른 하나는 밀접 결합 모델이다. 둘은 고체 내부의 전자들의 집단적인(collective) 거동을 두 가지 관점에서 바라 본 것이다. 흔히 물리적 현상은 간단한 모델에서 부터 점점 실제와 비슷한 조건을 부여하여 발전해 가는데 반도체 이론도 이와 같은 흐름을 가지고 있다. 준자유전자 모델의 경우 완전히 자유로운 전자의 설명에서 살짝 덜 자유스러운 전자로 바꿈으로써 에너지 밴드를 설명한다. 밀접 결합 모델은 단일 원자의 최외곽 전자처럼 묶여 있지만 약간의 에너지로도 떠날 수 있는 상태[2]에서 설명을 시도한다. 정리하면 준자유전자는 완전히 자유로운 전자로 부터 시작하고 밀접 결합은 강하게 묶인 상태로 부터 시작하여 둘 사이 어디쯤에 있는 실제 반도체의 상태를 설명하려 시도 한다. 이 둘을 모두 배운 학생은 두 개를 모두 배우면서 둘의 연관성을 찾기 힘들어 고민 할 수 도 있는데 이는 마치 어떤 현상을 거시적인 관점에서 부터 접근하는 방법과 양자역학 적인 관점으로 접근하는 방법 두 가지가 있는 것 처럼 반도체를 두 가지 조건으로 부터 발전시켰다고 생각하면 된다.

첫째인 준자유모델로 자유전자에 아주 약하고 규칙적인 전기적 포텐셜을 섭동으로 도입하면 자유전자가 가질 수 있는 에너지는 더이상 연속적이지 않고 불연속적으로 나타나게 된다. 이 모델은 양자역학의 슈뢰딩거 방정식을 규칙적인 포텐셜이 있을 때 풀어낸 해로 구했으며 처음 이를 유도한 블로흐는 지도교수인 하이젠베르그로 부터 고체물리학이 태동했다는 말을 들었다는 썰이 있다. 실제로도 그렇다. 블로흐 방정식이라고 이름까지 붙어있다.

나머지 하나는 밀접 결합 모델로 분자오비탈 이론과 유사하다. 뭐 거의 같은 논리적 흐름을 따른다. 분자오비탈 이론은 분자를 이루는 몇 개의 이온에 대하여 접근하지만 밀접 결합 모델은 수많은 이온들이 있을 때라는 점이 다르다. 규칙적으로 물질이 배열되어 있을 때 원자핵이 만드는 주기적인 에너지 우물에 강하게 속박되지 않은 (잠재적인) 자유전자의 파동함수를 구하면 단일 우물일때는 특정 에너지값들에서만 전자의 존재가 가능하지만, 우물들이 서로 간섭해 특정 값들이 모여 존재가 가능한 영역을 만든다. 이것을 원자의 경우에 적용시키면, 원자사이의 거리가 멀어서 원자들끼리 간섭하지 않을 때는 원자 내부의 전자는 양자화된 에너지 준위를 가지지만 원자간의 간격이 가까워져서 서로 간섭을 일으키게 되면 파울리의 배타원리에 의해서 영향을 주고 받는 원자들의 개수만큼 에너지 준위가 분리된다. 고체의 경우 원자간 간섭에 의해 오비탈의 에너지가 갈라지고, 각 원자들의 미세한 차이들이 모여 전자가 존재가능한 연속영역[3]인 에너지 띠(Energy band)와 전자가 존재하는것이 불가능한 빈 공간인 띠틈(band gap)[4]이 만들어진다. 이제 낮은 에너지 띠 영역에서부터 고체의 전자들이 채워지는데, 절대영도를 기준으로 에너지가 가장 큰 전자[5]가 채워진 에너지 띠를 원자가 띠(가전자띠. valence band), 전자가 채워지지 않은 빈 에너지 띠들 중에 가장 낮은 에너지 띠[6]를 전도띠(conduction band)[7]라고 한다.

3. 반도체의 전기적 성질

고체의 전기 전도성은 원자가 띠와 전도띠 사이의 띠 틈에 의해 결정된다. 도체의 경우 원자의 에너지 준위가 분리되어 에너지 띠를 만들때, 원자가 띠와 전도띠의 영역이 서로 겹쳐져서 띠틈이 존재하지 않아 원자가 띠의 전자가 약간의 열에너지 만으로도 전도띠로 건너 뛸수 있거나, 전자가 원자가 띠를 가득채우지 못해서 원자가 띠의 빈 공간이 전도띠의 역할을 한다. 그래서 실온 정도의 온도가 되면 자유전자가 엄청나게 많이 생겨 전기 전도성이 커지게 된다. 외곽전자결합이 약하고 띠에 여유도 많아 쉽게 움직이는 알칼리 금속이나 알칼리 토금속, 혹은 준위 중간에 빈틈이 많아서 전자가 이동하기 쉬운 전이 금속이 대표적인 도체이다. 부도체의 경우 원자가 띠와 전도띠 사이의 띠틈이 크기 때문에[8] 원자가 띠에 가득 찬 전자가 전도띠로 건너뛰지 못해 자유전자가 생기기 힘들어 전기 전도성이 작아진다.[9]

반도체의 경우 원자가 띠와 전도띠 사이에 띠틈이 2eV이하로 작아서 주변 온도에 의한 열에너지 만으로도 전자가 전도띠로 건너뛸수 있다. 이러한 에너지띠 구조의 특징으로 인해 온도에 의한 전기전도성의 변화가 크다. 실온정도의 온도를 기준으로 설명하자면, 실온에서는 약간의 전자가 전도띠로 건너와 있는 상태라 어느정도 전기가 통한다. 여기서 온도를 더 높여주면 더 많은 전자가 전도띠로 건너 뛰어 자유전자가 되고 반대로 온도를 낮춰주면 전도띠의 자유전자가 원자가띠로 떨어지면서 전기가 잘 통하지 않는 특성을 가지게 된다. 즉, 어떠한 온도를 기준으로 그 온도 이상에서는 전기가 비교적 잘 통하고, 필요한 값 미만으로 온도가 낮아지면 전기가 통하지 않는다는 것이다.[10]

반도체 소재는 크게 진성반도체(intrinsic semiconductor), 외인성 반도체(extrinsic semiconductor)로 구별하며, 외인성 반도체는 또다시 N형(Negative Type)반도체와 P형 반도체(Positive Type)로 나뉜다. 진성반도체는 ‘순물질’로 규정될 수 있는 물질로 이루어진 반도체이다. Si, GaAs 등이 이러한 반도체로 원소의 종류에따라 공유 또는 이온결합한다.

전하를 운반하는 운반자를 캐리어(Carrier)라고 한다. 공유결합이나 이온에 속박되어있던 전자가 열에너지 등에 의해 전도띠 에너지로 들뜨게 되면 전기퍼텐셜에 의해 전하를 운반할 수 있다. 그런데, 전도띠로 전자가 들뜨게 되면 원자가 띠에는 전자의 빈자리가 생기게 된다. 전자의 빈자리가 생기게 되면 원자가 띠에 있는 전자들도 움직일 수 있게 된다. 그러나 원자가 띠에는 전자가 거의 꽉들어차있어서 이 많은 전자들의 운동을 기술하는 것은 불가능하다. 따라서 전자의 빈자리를 하나의 입자로 보고 이것을 캐리어로 기술하는데, 이 캐리어를 양공(Hole)이라고 한다.

완전한(perfect) 진성반도체는 결합되어있던 전자가 결합에서 벗어나 자유전자가 됨에 따라 그 빈 자리인 정공 역시 같은 숫자로 생성되기 때문에 전자와 정공의 농도가 같을 수 밖에 없다. 그 농도는 전자의 총분포밀도(Population Density, 페르미-디락 분포과 관련되어있다.)를 전도띠 영역에서 적분하여 얻을 수 있다.

불순물을 첨가한 외인성반도체는 주 캐리어가 양공인 P형(Positive type) 혹은 주 캐리어가 전자인 N형(Negative type) 반도체로 나뉜다. 이 때 추가하는 불순물을 도펀트(Dopant)라고 하며, 주 캐리어가 양공인지, 전자인지는 도펀트의 원자가 특성에 의해 결정된다. 간략히 설명하면, 도펀트가 바탕물질(Matrix)보다 원자가가 높으면 결합하고 남는 전자를 전도띠로 내어놓아 전자가 주 캐리어가 되고, 도펀트가 바탕물질보다 원자가가 낮으면 오히려 결합을 위해 많은 전자가 필요하여 원자가띠의 전자를 흡수하므로 원자가 띠에 양공이 생겨 양공이 주 캐리어가 된다. 일반적으로 단위부피(1세제곱센티미터)당 바탕물질의 양은 10^22~10^23개의 원자가 있는데, 도펀트의 양은 보통 10^16정도이다. 따라서 수만개 중 1개의 도펀트 정도가 물질의 전기적 특성을 바꿔버리는 셈.

4. 반도체 소자

반도체의 전기적 성질을 이용하여 만든 장치.

P형 반도체와 N형 반도체를 활용하여 P-N접합을 통해 전류의 흐름이 일정한 방향으로 흐르게 하는 pn 접합형 다이오드나 P-N-P, N-P-N접합을 이용해 전기신호를 증폭시키는 바이폴라 트랜지스터(Bipolar Junction Transistor, BJT)를 만들어낼 수 있으며, 이외에도 금속을 n형 반도체 재료로 가볍게 도핑하는 쇼트키 다이오드, 금속과 융합한 CMOS, 그 하위부류인 FET나 MOSFET 등으로 만들어지며 이에 얽힌 발달과정이 현대 정보산업의 발전으로 이어졌다.

메모리 소자로는 현재 DRAM과 플래시 메모리가 주로 사용되고 있으며, 앞으로 예상되는 발전 방향은,현재 비휘발성 RAM인 MRAM(자기저항램)[11]과 PRAM(상변화램)[12]이 연구중이며, MRAM은 이미 우주분야나 블랙박스와 같은 최첨단 중의 최첨단의 분야에서 사용되기 시작했다.

MRAM과 PRAM은 속도는 DRAM과 같지만 전원 공급이 중단되어도 데이터를 상실하지 않고 수명도 사실상 무한하다. 말그대로 궁극의 저장매체인 것이다. 만일 개인용 컴퓨터 시장[13]에서 SSD가 하드디스크를 완전히 밀어낼 시점이 다가오면 MRAM이나 PRAM을 이용한 저장매체가 나와 SSD의 자리를 위협할 것이다.

삼성전자에서는 PRAM 양산을 위한 연구를 진행하고 있으며 MRAM은 독일의 반도체 연구소인 PTB에서 양산 알고리즘을 연구하고 있다. FeRAM(강유전체 램)이라는 것도 있지만, 시제품을 만들어 놓고 보니 개념(이론)과는 너무도 다른 결과를 보여줬다. 즉, 속도도 예상했던 DRAM만큼 나오지도 않았고 고용량을 위한 고도집적화도 거의 불가능해 지금은 시망, 좆망 테크를 타고 있는 중. 참고로, 일본 후지쯔에서 어찌어찌 해보겠다고 강짜를 놓다가 역시 좆망.

MRAM과 PRAM의 경우는 프로토타입 단계는 이미 2000년대 초반에 지났고 현재는 소자의 고도화, 양산화를 위한 연구가 진행중에 있다.[14][15] 즉, 학계의 손을 떠나 기업 주도로 연구ㆍ개발이 이루어지고 있는 것. 2018년 시점에 PRAM은 3D XPoint라는 이름으로 인텔에 의해 상용화가 되기에 이른 상태이다.

사실, MRAM과 PRAM을 대체할 반도체도 기다리고 있다. 바로 RRAM(저항메모리)와 NRAM(나노램)이 기다리고 있다. MRAM이 박막의 스핀배열이 평행/반평행인지에 따라 저항이 변화는 스핀밸브현상 혹은 거대자기저항(GMR)을 이용한 소자라면, RRAM은 멤리스터라고 불리는 물질을 사용하여 일반적으로는 전기를 잘 통하지 않지만 (높은 저항) , 유전체 사이의 전도 path를 일시적으로 형성하여 저항을 낮출 수 있다.

또, 개념상 제시된 미래의 RAM에는 밀리페드(Millipede) 반도체와 경주트랙(Racetrack) 메모리라는 것도 있다. 가장 멀리있는 가시거리내 기술로는 Nano Magnets – 분자단위 자기적 정보 저장기술로 2012년 6월, 분자단위로 자기 정보를 바꾸는 단계까지 와있다.# 즉, 지금의 SSD개념이 궁극적인 저장매체라는 착각을 해서는 안된다는 것. 반도체 공학의 세계는 끝이없으므로, 계속 공부를… 참고로, 카이스트 전기및전자공학과 명 모 교수가 수업시간에 상술한 반도체들의 상용화 예측 연도를 강의한 바 있는데 MRAM이나 PRAM은 2020년대 초중반, RRAM은 2020년대 후반, 밀리페드는 2030년대, 레이스트랙은 2050년대, 나노저장장비는 2000년대 중후반으로 제시했다. MRAM에서 RRAM간의 상용화 주기가 약간 짧은 것은, 사실상 RAM의 물리적 구조를 개선한 것이기 때문이다. 밀리패드 부터는 기존의 RAM과는 완전히 다른 새로운 구조이다.

현대 반도체 산업의 중심인 Si는 석영의 주성분으로서 지각에 가장 많은 2대 원소 중 하나이며 암석의 주요 성분이기 때문에 현대를 철기시대에 이은 새로운 석기시대라고 제3 석시대?[16] 농담 삼아 말하는 경우도 있다.

참고로, 반도체 분야에서는 학계의 동향을 항상 신뢰할 수 있는 것은 아니다. CPU 공정 단위가 수십 나노미터 단위로 내려가기 전까지 학계에서는 지속적으로 40nm 이하[17]의 양산이 불가능하다는 주장이 강했지만, 기업의 공밀레 정신으로 그것을 극복해 냈다[18]. 또한 학계는 IGZO트랜지스터가 차세대 디스플레이 구동 소자로 연구되기 전 까지 나노결정 실리콘[19]을 매우 주목했으나, 시제품은 기존 디바이스의 단점만 모인 영 쓸모 없는 것이었다.

5. 반도체 산업

6. 관련항목

‘트랜지스터’에 관한 나무위키의 내용 – 2018년 9월 30일 현재

1. 개요

명실상부한 전자공학의 꽃.

Transfer + Resistor = Transistor

전기 스위치와 증폭 작용을 하는 반도체 소자.

보통 반도체라고 불리우는 물건이라고 생각하면 쉽다.[1] 반도체 물질을 적극 이용해서 전기의 흐름을 제어하고, 정보를 처리한다. 보통 트랜지스터는 발이 3개 달려있는데, 가운데에 있는 발이 스위치 역할을 해서 이곳에 전기신호를 보내 양 옆에 달린 발이 연결되기도 끊기기도 한다. 전자공학에서 가장 기초적인 부품으로 트랜지스터를 조합해서 AND, OR, NAND, NOR, XOR 등의 논리 게이트를 만들 수 있고, 이 논리게이트를 다시 조합해서 덧셈 연산기, 기억장치 등을 만들 수 있다. 이 트랜지스터를 좀 더 조밀하게 만들어 작은 칩에 넣은 것을 집적 회로(IC)라고 한다. 초기에는 트랜지스터 수 천~수 백만개를 집적한 집적회로만 있었지만, 현재에 이르러서는 수 억개~수 십억개는 기본으로 때려박아서 만든다. 우리가 흔하게 사용하는 CPU, GPU, 플래시 메모리[2], RAM 전부 트랜지스터를 이용해서 만든 것이다. 한마디로 현대 사회를 지탱하는 컴퓨터 전반은 전부 트랜지스터로 이루어져있다고 보면된다.

n은 네거티브이고 p는 포지티브이다.

2. 종류

2.1. 접합형 트랜지스터 (BJT)

n-p-n형 BJT(Bipolar Junction Transistor)

아래 수도꼭지 비유 설명이 이해하기 쉽다.

1947년 벨 연구소의 H.W.Brattain과 J.Bardeen, W.Shockely가 게르마늄을 이용해 최초로 제작하였다. (이에 대한 공로로 세 사람은 1956년 노벨물리학상을 수상하였다.) 조립형 전자 키트 등을 사면 쉽게 볼 수 있다(새까만 삼발이 부품).[3] 실리콘 웨이퍼에 수 차례 도핑을 거치면 완성되는 구조라, 옥사이드를 길러야 하는 MOSFET보다 제조하기 쉽다는 장점이 있다. 작동 원리는 다이오드와 동일한데, 전하를 공급하는 이미터(Emitter)가 더 붙어있는 것이다.

우선 p-n-p형 접합형 트랜지스터를 예로 들어보자. 그리고 이때 p-n-p의 각 역할을 emitter-base-collector라 하자. 이 경우 왼쪽의 p-n 접합에 정방향 전압[4]를 주면 전류가 흐르지만, 오른쪽 n-p 접합인 베이스-컬렉터(Base-Collector)에 역방향 전압도 걸려진다. 이때 emitter-base측에 충분한 전압을 걸면 (Emitter-Base 접합은 순바이어스) 이미터의 hole(양공)들이 베이스로 주입되고 베이스의 전자가 이미터로 (상대적으로 적은 양이) 주입되며, 베이스 내부에서는 Diffusing(확산) 현상으로 컬렉터 쪽으로 양공이 이동해 컬렉터에 양공이 수집된다. (이 때 이미터에서 베이스로 주입되는 양공의 양이 베이스에서 이미터로 주입되는 전자의 양보다 훨씬 더 많은 것이 바람직 하며, 고농도로 도핑된 이미터와 저농도로 도핑된 베이스를 사용하여야한다. 혹은 베이스를 물리적으로 얇고 적게 하거나.)

베이스 내부에서 Diffusing(확산)하는 양공들 중 극히 일부분이 베이스의 전자와 결합하는데 이는 컬렉터에 수집되는 양공들에 비해서 아주 작은 비율이다. 하지만 이로 인해, 과잉소수 캐리어(이 경우에는 양공) 농도 분포가 직선이 아닌 곡선형태가 된다. 결론적으로 양공이 Emitter에서 Collector 방향으로 이동되므로, 전류의 방향은 Emitter에서 Collector 방향이다. 앞서 설명한 내용은 베이스-이미터가 순바이어스, 베이스-컬렉터가 역바이어스된 경우이다.

만약 베이스-이미터접합이 역바이어스 된다면, 이미터에서 베이스로 전자가 충분히 주입되지 못하므로, 전류의 흐름이 차단된다.(Cut-off Mode)

만약 베이스-이미터접합과 베이스-컬렉터접합이 모두 순바이어스 된다면, 이미터에서 베이스로 양공이 수집되고 Diffusing 현상이 발생하는 동안, 컬렉터에서 베이스로도 양공이 수집된다. 이 때, 베이스에 전자농도가 높아지기 때문에 포화상태라고 한다.(Saturation Mode) 포화 상태에서는 전류의 흐름이 서로 상쇄되므로, 컬렉터-이미터 전압은 0.1~0.2V 정도로 유지된다.

공돌이들 용어 다 걷어내고 좀 많이 생략한 거지만 간단하게 예시를 들어 설명해보자.

에미터(Emitter, 방출기)는 수도관이고 콜렉터(Collector, 수집기)라고 하는게 수도꼭지고 베이스가 수도밸브라 보면 된다. 수도밸브가 돌아가는 정도에 따라 변하는 수압을 전압으로 이해하면 된다. 근데 저 밸브가 좀 물이 새는 밸브라서 에미터에서 콜렉터로 빠질 때 물이 조금, 아주 조금 줄어든다고 지금 위에서 세번째 문단에서 설명하고 있는 것이다.

그럼 스위치 작용은 설명이 되는데 증폭 작용은 사실 증폭하는 게 아니라 작은 힘으로 큰 힘을 제어하는 것이다. 이미터-콜렉터 사이를 흐르는 커다란 전류를 베이스라고 하는 작은 밸브로 조절하는 것이다. 트랜지스터를 통과했다고 1볼트가 2볼트가 되는 건 아니다. 오히려 전압은 줄어들어버린다. 다만 베이스 전압이 0~1볼트 사이를 움직일 때 이미터-컬렉터를 통과하는 전압은 0~12볼트 사이를 왔다갔다한다. 물론 베이스가 물이 좀 새는 밸브라서 정확히 똑같게 따라하지는 못하는데 그 차이를 줄인 게 고급 트랜지스터라고 이해하면 된다.

마지막으로 수도꼭지와 트랜지스터의 다른 점이 수도꼭지는 사람 힘으로 밸브를 돌리지만 트랜지스터는 전압으로 돌린다. 전압이라고 하는 건 전위차 즉 상대적인 개념인데 그래서 트랜지스터 회로는 이미터 단자를 공통 음극(NPN기준)으로 사용한다. 이미터의 전압을 0볼트로 간주하겠다는 의미(보통 이미터는 접지까지 공유하므로 실제로 0볼트일 때가 많다). 그래서 전압 차이가 아주 크게 나는 회로에서는 트랜지스터를 사용할 때 조심해야 한다. 이미터-콜렉터 사이에서 어떤 이유에서든 엄청난 전류가 흘러버리면 이미터쪽 전압이 확 변할 수 있는데 이미터-베이스간에도 회로가 연결돼있으므로 이미터-베이스 사이의 전위차가 그 회로가 견딜 수 있는 한도를 넘어 확 튀는 경우가 있다. 보통 이미터-베이스 사이에 있는 회로는 민감한 회로들이라 이런 식으로 확 튀는 전류가 들어가버리면 그냥 타버린다. 그래서 큰 전류를 제어하는 곳에서는 트랜지스터 말고 다른 소자들을 사용하는데 이 이상은 전문적인 영역.

2.2. 전계 효과 트랜지스터 (FET)

2.2.1. 접합형 전계 효과 트랜지스터 (JFET)

1925년 릴리엔필드가 최초로 개발해 특허를 등록하였다. 최초의 트랜지스터. 당시에 개발된 FET는 화합물 반도체에 게이트 전극을 꽂아 전류가 흐르는 통로의 폭을 조절하는, 현대의 MESFET과 같은 동작을 하는 물건이었다. 릴리엔필드는 이 소자가 동작하는 것은 입증했지만, 동작 방법은 잘 설명하지 못했다(이걸 제대로 설명하려면 고체물리와 양자역학에 대한 이해가 필요하다). 이후 이 소자는 현대식의 JFET로 발전한다.

일반적으로 교과서에서 소개하는 JFET는 PNP나 NPN의 구조로 만들어진 소자를 소개한다. 이렇게 소자를 세로로 쌓아두고 중간의 소자 양 옆에 가로로 소스, 드레인 전극을 달아둔 것이다. 쉽게 말하면 위 BJT그림에서 세 단자를 왼쪽으로 한 칸씩 움직여보자.

반도체 PN접합의 특성상, 서로 다른 두 개의 반도체를 붙여 두면 상대쪽에 전하가 생기지 못 하는 Depletion Region이 생겨나는데, 이 동네는 터널링(에너지 준위 차이가 크고, 전도할 길이가 너무 좁으면 전자/정공이 지나가지 못 하는 지역이라도 그대로 ‘워프’ 해버리는 현상)을 이용하지 않는 이상 지나갈 수 없다. 또한 이 지역의 깊이, 혹은 넓이는 PN양극의 전위차가(역방향일 경우) 높으면 높을 수록 커진다.

즉, 가운데 지역 양 옆에 전극을 두고, 위 아래에는 게이트 전극을 두어 전압을 변화시키면 이 Depletion Region을 크게, 작게 변화시키면 소스-드레인간의 통로를 자유자재로 여닫아 트랜지스터로 만들 수 있는 것이다.

대략적인 작동 원리는 이렇고, 이렇게 단순하게 만든 이유는 역시나 그 당시 공정 기술이 딸렸기 때문. 게다가 군용 무기같은 경우는 안정성이 높아야 하므로 세밀한 고급 공정 보다는 단순한 공정을 사용한 물건들이 필요하기에 이렇게 만들어졌다.

JFET는 특성상 소자의 크기만 크면 큰 전류도 다룰 수 있고, 진공관과 전류-전압 특성이 유사해 오디오 등의 고출력이 필요한 전자제품에 주로 사용된다(MOSFET은 게이트 절연층의 두께 문제로 크게 만들기가 매우 어렵다). 하지만 집적회로가 나오면서부터는 누설전류가 너무 커서(역바이어스를 걸어도 PN접합에는 전류가 흐르고, 실수로 정바이어스라도 걸리는 날에는 소자가 바로 망가진다) 사용을 하지 않는다.

2.2.2. 금속 산화물 반도체 전계 효과 트랜지스터 (MOSFET)

n형 MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)

집적회로가 나타날 수 있게 만든 트랜지스터이다. 소스와 드레인의 도핑에 따라 n형과 p형으로 나뉘고 n형과 p형이 나란히 있는 CMOS가 존재한다. 개발자는 벨 연구소에 근무하던 한국계 미국인 강대원 박사 등. 최초의 디자인은 그냥 실리콘 덩어리에다 옥사이드 깔아 놓고 메탈을 꾹 눌러 놓은 루티드스러운 형태였다. 발표된 순서는 BJT보다 먼저였으나, 실리콘과 옥사이드 사이의 인터페이스 스테이트를 제대로 줄이지 못 했기에 상용화는 지지부진이었다. 그러나 이후 실리콘 위에 옥사이드를 얻는 게 아니라, 실리콘 자체를 리액터에 넣어 산화시키는(수증기, H2O기반의 프리커서를 쓰면 wet, H2, O2 따로 넣으면 dry)공정이 개발된 이후 본격적으로 IC의 시대가 열린다. 여기에 가장 큰 공헌을 한 인물은 텍사스 인스트루먼츠의 잭 킬비.

MOSFET의 작동 원리는 다음과 같다. 일반적으로 많이 사용되는 n-channel MOSFET의 경우, 게이트에 양의 전압을 인가하여 Substrate Silicon에 공핍층을 형성한다. 이 때 게이트 전압이 Threshold Voltage, 즉 문턱 전압을 넘게 되면 Oxide-Semiconductor Interface에 Minority Carrier인 전자가 밀집하게 되어 채널을 형성하고, 이 얇은 레이어를 Inversion Layer라고 부른다. 소스와 드레인 전극은 p-substrate에 n+로 도핑하여 형성되므로, 소스에 GND, 드레인에 드레인 전압 VD를 인가하여 전계를 형성하면 드레인 전류 ID가 VD에 의해 선형적으로 증가하는 꼴을 보인다. 한편 VD가 VG(게이트 전압) – VT(문턱 전압)에 도달하게 되면 더이상 전류량의 증가는 일어나지 않는다. 이 때 VG-VT를 Pinch-off Voltage라고 한다.

드레인에 축전기를 연결하면 DRAM이 된다.[5] 축전기에 전하가 존재하면 1, 전하가 없으면 0이다. 사실상 우리가 보고 있는 TFT LCD모니터도 이와 동일한 메커니즘으로 작동한다. 다만, 축전기 역할을 하는 게 리퀴드 크리스털이다.

그리고 게이트쪽에 유전막 층을 더 넣고, 전극을 하나 더 넣어, 이 유전막에 전자를 넣었다 뺐다 하면 생기는 문턱전압의 차이로 데이터를 쓰고 읽으면 플래시 메모리가 된다. 플래시 메모리에서는 유전막을 플로팅 게이트라고 하며 일반적인 이산화실리콘 대신 질화실리콘을 사용하는 경우가 많다. 플로팅 게이트에 전자를 넣으면 문턱전압이 높고 전자가 없으면 문턱전압이 낮다. SLC (Single Level Cell) 플래시 메모리의 경우, 예를 들어 문턱전압이 바뀌는 범위가 0.5 V 부터 1.5 V 라면 1 V 가량의 전압을 가해줬을 때 트랜지스터가 작동하면 1, 작동하지 않으면 0 이다. MLC (Multi Level Cell) 플래시 메모리는 문턱전압이 아주 낮으면 11 덜 낮으면 10 좀 높으면 01 아주 높으면 00 이런 식이다.

CPU나 GPU, DRAM, 플래시 메모리 공정의 nm 단위 숫자는 MOSFET의 크기[6]를 나타내는 것이며 숫자가 작을수록 좋다. 공정이 미세화되면 누설전류에 관한 문제가 심각해 지기 때문에 SOI[7] 기술 혹은 하프늄이나 지르코늄, 티타늄 산화물을 이용한 고유전율 유전막[8] 기술이 적용되어야 한다[10][11]. HKMG로는 감당이 안될정도로 공정이 미세화가 되자 소자를 물고기 지느러미 처럼 만든 FinFET이 나왔다. 3D라고 해서 FET를 쌓아올린것으로 생각할수 있으나 그냥 FET를 3D로 만든것에 불과하다. 하지만 물리학적 한계때문에 30nm미만 공정은 모두 이 방식으로 만들어지고 있다.

21세기 들어서 High 파워 반도체를 제외하면 아날로그 집적회로는 거의 모두 CMOS 로 설계된다고 봐도 무방하다.

2.2.3. 박막 트랜지스터 (TFT)

LCD나 AMOLED 같은 평판 디스플레이의 픽셀 구동 소자로 쓰이는 트랜지스터이다. 녹는점이 낮은 유리 기판(대략 5-600도 정도다. 실리콘 웨이퍼 공정은 1000도(섭씨)이상 올라가는 경우도 매우 많다.) 위에 단결정 실리콘을 올리기는 거의 불가능 하기 때문에 많은 경우에 채널층에 비정질 실리콘이 사용된다. 따라서 채널층의 유효 이동도가 MOSFET 보다 낮기 때문에 MOSFET에 비하면 성능은 떨어진다.

한편, 해상도를 늘리고 화질을 개선시키기 위해 a-Si:H TFT의 field effect mobility를 늘리려는 시도가 여러 가지 시도되었으나 그 중 가장 각광받은 것은 Polysilicon TFT다. 이 Polysilicon은 사실 결정질(Crystalline)실리콘이 마치 기워입은 옷 처럼 배치되어 있는 것으로 기워버린 부분에 트랜지스터의 채널이 걸치지 않으면 이론상 결정질 실리콘을 이용해 만든 MOSFET과 거의 비슷한 성능을 내기에 전류 구동 능력을 획기적으로 끌어올릴 수 있어 고집적 화소+고화질 디스플레이를 구현하기에는 최적의 조건을 마련해 준다. 실제로 이걸 이용한 LCD 기반 프로젝터 등이 일본 회사들에서 출시되었다.

다만, 이놈을 제작하기 위해서는 기존 채널층의 비정질 실리콘을 엑시머 레이저 어닐링 같은 공정을 통해 결정화 시킨다(이렇게 결정화 시킨 그러나 레이저 애블레이션 과정은 매우 돈이 많이 들어가는 공정이라 단가가 비싸다.) 게다가 레이져로 표면을 긁어야하는 공정인지라 화면 크기가 크면 클 수록 단가는 더더욱 올라가게 되어 버렸고, 이는 대형 TV나 심지어 스마트폰 정도의 크기 디스플레이를 제작한다 할 지라도 가격 상승을 불러온다[12]. 또한 레이저로 화면을 긁는 과정에서 실리콘이 부분적으로 결정화가 되는 방식이기 때문에 Grain boundary가 제각각이므로 Uniformity의 문제가 발생하여 화면의 밝기가 일정하지 않은 Mura 현상이 발생하기도 한다. 게다가 OLED의 발견으로 대규모 화면을 더 저렴하게 구현할 수 있게 되었고, 이를 기존 LCD 화면 구동 방식[13][14]을 접합해 Active Matrix OLED 라고 부르기 시작한다. 문제는 이 OLED를 구동이나마 시킬 수 있는 성능을 가진 Polysilicon TFT의 경우, 대형 화면을 제작하기 위해 거하게 제작하면 단가가 뛰어버린다. 덕분에 이 제작단가를 줄이기 위해 여러 곳에서 시도를 해 보긴 했지만…[15]

어쨋든 이 백플레인(Backplain 이라는 요상한 용어인데, 디스플레이 발광 소자나 디텍터 감응 소자(?)를 제외한 부분을 보통 이렇게 지칭한다.) 제작 단가를 줄여보기 위해 태양 전지에 사용하던 마이크로 크리스탈린 실리콘이나 나노크리스탈린 실리콘을 이용한 TFT를 만들어 보려는 시도도 존재했으나 예상보다 성능이 좋지 않아 사장되어 폭망했다.[16]) 인듐 갈륨 아연 산화물로 대표되는 비정질 금속 산화물로 바꾸는 시도가 이루어지고 있다. 이 쪽 연구로 유명한 것은 역시 일본. 실제로 샤프가 최초로 시제품을 출시했으며, 메탈 옥사이드 물질 연구의 대가 또한 일본에 있다. 그러나 실제 제품화하는 것에서는 2017년 현재 LG 디스플레이가 상위에 있다. 자세한 내용은 Oxide TFT 문서를 참조하기 바란다.

참고로, 비정질 실리콘 트랜지스터의 경우에는 P타입이 없다. 비정질 실리콘 자체의 물성 때문에 정공의 이동도가 안습 오브 캐안습이기 때문[17]. 더 웃기는 건 nMOSFET의 경우는 베이스가 P타입인데, 비정질 실리콘의 경우는 자체적으로 약한 nType 실리콘의 형질을 지닌다. 그럼에도 불구하고 nMOSFET으로 구동된다. 이놈을 p-Type 을 이용해 구현할 경우 Threshold Voltage가 너무나 높아지기에 어쩔 수 없는 선택. 즉, TFT는 Accumulation Mode에서 작동한다.

3. 기타

아래와 같은 트랜지스터들도 있지만, 일반인이 보기는 매우 어렵다.

UJT : PN접합이 1개뿐인 트랜지스터. 다이오드와 같은 모양인데, 다이오드의 한쪽 전극을 두개로 쪼개 각각의 끝에 전극을 붙인 형상을 하고 있다. 이 트랜지스터는 음의 저항(아니 이게 뭔 개소리야 라고 할지도 모르겠지만, 이 소자의 V-I 곡선은 N자 모양으로 형성된다) 특성을 갖기 때문에 발진기로 쓰인다.

IGBT : 항목 참조. 바이폴라 트랜지스터의 베이스 전극이 절연되어 있다.

MESFET : 쇼트키 효과를 이용한 트랜지스터. NIN(n형 도핑영역 사이에 진성반도체를 끼워넣은 형상)구조의 진성반도체 영역에 게이트 전극을 직접 붙인 형상을 하고 있다. GHz 급의 초고주파 영역에서 사용된다. 사실 릴리엔필드의 특허는 이 트랜지스터와 더 가깝다.

그 밖에 수십 ~ 수백 GHz급의 초고주파 영역에서 사용되는 HEMT(High Electron Mobility Transistor), HJT(Hetero-Junction Transistor) 등이 있다.

그리고 자세한 건 전자회로 및 초고주파공학 관련 전공책도 좋지만, 그게 어려운 일반인은 물리1을 보면 된다.

혹시 시중에 나온 회로이론 책을 뒤지다가 트랜지스터 항목이 안나와서 난감 했다면, 반도체소자 내지 전기/전자공학개론 앞장을 펼쳐 반도체가 나온 항목을 찾아봐도 좋다.[18]

트랜지스터라디오는 합성어로 취급되어 붙여쓴다.

참고로 트랜지스터의 극성을 잘못 꽂으면 트랜지스터가 매우 뜨거워져서 화상을 입을수 있다.

https://m.post.naver.com/viewer/postView.nhn?volumeNo=16728265&memberNo=42802432

물에 강한 반도체 물질 ‘페로브스카이트’, 드디어 나왔다!

차세대 태양전지의 강력한 후보 물질

” 페로브스카이트 “

· 육방면체의 특별한 구조를 가진 반도체 물질

· 값싸고 쉽고 신속하게 합성할 수 있는 물질

· 빛을 전기로 바꾸거나 전기를 빛으로 바꾸는 특성

· 각광받는 차세대 태양전지 재료

그러나

“물에 취약하다는 최대 단점!”

수분에 취약한 ‘페로브스카이트’

페로브스카이트는 육방면체의 특별한 구조를 가진 반도체 물질로 고체 상태의 조명, 광검출기, 레이저 등의 산업 분야에 응용되고 있다. 특히 태양전지로 활용하려는 연구가 활발하게 진행되면서 광전변환효율이 크게 개선돼 차세대 태양전지 물질로 주목받고 있다.

그러나 이 물질은 수분에 취약하여 물이 존재할 경우 광전변화효율이 급격히 감소해 안정성이 떨어진다. 따라서 태양전지뿐 아니라 광전자공학, 생의학 및 촉매 분야 등 다양한 분야에서 페로브스카이트를 사용하려면 물이 있는 환경에서도 안정한 성질을 유지하는 게 중요하다.

이런 문제를 해결하기 위해 페로브스카이트 물질이 물에 반응하지 않도록 하는 다양한 방법이 시도되었지만 완벽하게 내수성을 가지는 페로브스카이트 물질은 아직 발표되지 않았다.

내수성 페로브스카이트 합성법 개발

최근 울산과학기술원(UNIST) 자연과학부 화학과 김광수 특훈교수 연구팀은 페로브스카이트 표면에 일종의 ‘방수막’을 만드는 합성법을 개발, 이 방법으로 만든 페로브스카이트는 6개월 이상 물 속에 담가도 고유의 특성을 유지한다고 밝혔다.

김광수 교수는 “페로브스카이트는 값싸고 쉽고 신속하게 합성할 수 있는 물질이라 소재로서 각광받고 있다”며 “물에 취약하다는 최대 단점을 완벽하게 잡은 만큼 태양전지, 발광다이오드(LED), 강유전체소재 등에 산업적으로 적용할 날도 빨라질 것으로 기대하고 있다”고 말했다.

‘수산화납 보호막’을 형성하는 새로운 합성법

연구팀은 ‘염기성 증기 확산법’을 이용해 페로브스카이트 표면에 ‘수산화납 보호막’을 형성시켜 ‘유-무기 복합/페로브스카이트’의 내수성을 높였다. 페로브스카이트 물질을 합성하는 방식을 새롭게 제안해 자연스럽게 보호막이 생기게 만드는 방식이라, 외부에서 다른 물질을 가져오지 않아도 된다.

이번에 개발한 내수성 페로브스카이트 물질 합성법은 간단하다. 우선 작은 유리병과 큰 유리병을 준비한다. 작은 유리병에는 산성 용액에 녹아 있는 페로브스카이트 재료로서 할로겐 산-금속 할라이드 전구체 염을 놓고, 큰 유리병에는 염기성 용액인 메틸아민을 담는다.

그런 다음 작은 유리병의 뚜껑을 연 채 큰 유리병 속에 넣고, 큰 유리병의 뚜껑만 닫는다. 이렇게 되면 메틸아민이 증발하면서 작은 유리병 속으로 들어가는데, 이때 페로브스카이트 물질이 합성되면서 내부에 자연스럽게 수산화납 보호막이 형성된다.

페로브스카이트 표면에 형성된 수산화납 보호막은 표면층을 환원시킨다. 또 구조가 안정적이라 수분과 만나도 반응하지 않는다. 그 덕분에 페로브스카이트 내부로 침투하는 물 분자를 막아 페로브스카이트의 내수성과 수명을 현저히 증가시켰다.

물의 산도(pH)와 상관없는 안정적인 특성

아타누 자나(Atanu Jana) 박사는 아타누 자나 박사는 “두 개의 유리병에 각각의 재료를 담아두고 10일 정도 두면 자연스럽게 수산화납 보호막을 가진 페로브스카이트가 합성된다”며 “수산화납은 안정적인 구조라 수분을 만나도 반응하지 않고, 물질 내부로 물이 침투하지 않게 막는다”고 설명했다.

이렇게 개발한 물질은 2017년 9월 물 속에 넣어 1년이 지난 현재 시점에서도 페로브스카이트 본연의 특성을 유지했다. 즉, 높은 에너지 전환 효율, 에너지 띠 조절을 통한 형광 특성이 손상되지 않았다. 이는 긴 수명을 가진 광전자기기나 태양전지, 발광다이오드 등 다양한 분야로 적용 가능하게 만든다.

광전자기기, 태양전지, 발광다이오드 분야 적용

자나 박사는 “새로 개발한 내수성 페로브스카이트는 거의 완벽하게 물을 막기 때문에 물의 산도(pH)와 상관없이 안정적인 특성을 보인다”며 “합성법 또한 간단하기 때문에 대규모 합성이 가능하다는 장점이 있다”고 강조했다.

김광수 교수는 “그동안 페로브스카이트 물질과 철저히 분리돼야 했던 ‘습한 환경’이라는 조건에서도 페로브스카이트가 사용될 가능성을 열었다”며 “페로브스카이트가 기존과는 다른 새로운 분야에 사용되는 시작점이 될 것”이라고 기대했다.

한편, 이번 연구는 미국화학회(ACS)에서 발행하는 에너지 분야의 국제학술지인 ‘ACS 에너지 레터(ACS Energy Letter)’ 8월 13일자에 게재되었으며, 게재 2주 만에 ‘8월 중 가장 많이 읽은 논문’에 선정되었다.

https://m.blog.naver.com/ibs_official/221362585239

빛 쪼여 2차원 반도체 성능 대폭 높인다!

-가시광선 레이저로 수초 만에 원자두께 반도체 대면적 도핑-

-단일 집적회로 구현도···2차원 반도체 상용화 길 열어!-

거미에 물린 ‘스파이더 맨’, 특별한 슈트를 훔쳐 입은 ‘앤트맨’…. 영화 속 슈퍼히어로들은 특별한 능력을 얻어 인간을 넘어서는 능력을 갖게 됩니다. 반도체도 마찬가지입니다. 반도체는 순수한 상태에서는 전기가 거의 통하지 않습니다. 하지만 외부 불순물을 소량 첨가하면 전기가 통하는 물질이 됩니다. 이 기술을 ‘도핑’이라 합니다. 슈퍼히어로의 아이템처럼 도핑은 반도체를 전자기기용 소자로 사용하기 위한 필수 공정입니다.

휴대용 전자기기의 발전과 함께 과학자들은 성능은 높고, 크기는 더 작은 전자기기를 개발하려는 노력을 이어왔습니다. 두께가 거의 없는 ‘2차원 반도체’는 이를 완성하기 위한 열쇠로 꼽힙니다. 문제는 기존 도핑 기술을 2차원 반도체에 적용할 수 없다는 것이었습니다. 원자 두께의 2차원 반도체에 불순물을 주입하면 깨질 가능성이 있고, 농도를 섬세하게 조절하기 어렵다는 점이 상용화의 걸림돌이 됐습니다.

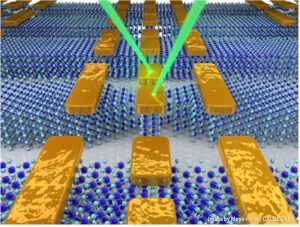

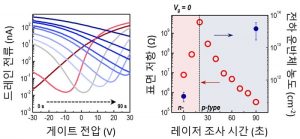

기초과학연구원 원자제어 저차원 전자계 연구단은 빛만을 이용해 외부 불순물 주입 없이도 2차원 반도체를 도핑할 수 있는 기술을 개발해 이 문제를 해결했습니다. 연구진이 개발한 ‘레이저 도핑’ 기술은 수 초간 레이저를 조사하는 것만으로 대면적 도핑이 가능합니다. 기존 전무했던 2차원 반도체 도핑 기술을 개발한 것은 물론, 기존 도핑 기술보다 더 빠르고 경제적인 도핑이 가능하다는 의미입니다.

도핑을 통해 반도체의 전도도를 높일 수 있는 방향은 두 가지입니다. 하나는 전자의 수를 늘리는 것.전자가 많아지면 원자핵과 결합하지 못한 잉여 전자들이 소재 내부에서 자유롭게 이동할 수 있기 때문입니다. 다른 방법은 정공(전자의 빈자리)의 수를 늘리는 것입니다. 이 경우엔 전자가 이웃한 빈자리로 이동하는 과정에서 전자의 흐름, 즉 전류가 생긴다. 전자가 많은 반도체를 n-형, 정공이 많은 반도체를 p-형이라 합니다.

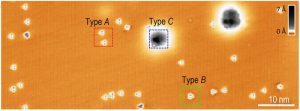

조문호 IBS 원자제어 저차원 전자계 연구단 부연구단장(포스텍 신소재공학과 무은재 석좌교수) 팀은 레이저 도핑을 통해 반도체를 p-형으로 도핑하는 데 성공했습니다. 서승영 연구원(포스텍 신소재공학과, 제1저자)을 비롯한 연구진은 주사터널링현미경(STM)으로 2차원 반도체를 관찰하며, 그 표면에 파장 532nm의 초록색 레이저 빛을 수 초간 조사했습니다. 주사터널링현미경은 맹인이 점자를 통해 글을 파악하는 것처럼, 얇은 금속 탐침을 이용해 표면의 요철을 읽어 원자 수준의 해상도로 이미지를 얻는 기술입니다.

주사터널링현미경(STM)으로 관찰한 원자층 2차원 반도체의 모습. 레이저 조사 이후 반도체 표면과 내부엔 결함(Type A, B, C)이 형성된다. 이 공간에 정공이 주입되며 p-형 반도체로 도핑된다.

이어 연구팀은 개발한 도핑 공정을 이용해 다양한 2차원 반도체 회로를 제작하는 데도 성공했습니다. 이텔루륨화몰리브덴(MoTe2) 화합물에 레이저 도핑을 접목해 2차원 양극성 접합 트랜지스터(Bipolar Junction Transistor), 2차원 광전압 변환기 등을 구현했습니다. 원자층 2차원 반도체를 재료로 도핑하고, 실제로 구현으로까지 이어진 첫 사례입니다. 제작된 반도체 회로는 매우 우수한 전류 증폭 성능을 보였습니다.

이번 연구를 이끈 조문호 부연구단장은 “반도체 물질과 빛의 상호 작용에 대한 기초 과학 연구가 차세대 반도체 회로 응용 기술로 바로 환원됐다는 데 의의가 있다”며 “이러한 기초과학-응용기술 순환 일체형 연구는 미래 기술 개발에 있어 새로운 가치 창출 방식의 핵심이 될 수 있다”고 밝혔습니다.

이번 연구 성과는 국제학술지 ‘네이처’의 자매지인 ‘네이처 일렉트로닉스(Nature Electronics)’ 9월 14일(한국시간)자 온라인 판에 실렸습니다.

문외한을 위한 시스템반도체 총정리

3대 키워드 비메모리,인공지능, 뉴로모픽

정부와 기업이 앞으로 10년동안 시스템반도체 연구개발에 1조 원을 투입하고 전문이력을 채용하겠다고 밝혔다. 게티이미지뱅크

진격의 거인, 아니 진격의 반도체다. 정부와 국내 기업이 10년째 제자리걸음을 하고 있는 시스템 반도체 산업을 2030년 파운드리 분야 세계 1위, 팹리스 분야 글로벌 시장점유율 10%으로 높이기 위해 나섰다. 정부는 앞으로 10년 동안 시스템반도체 연구개발(R&D)에 예산 1조 원을 투입해 전문 인력 1만7000명을 양성할 계획이다. 삼성전자도 2030년까지 133조 원을 투자하고 전문 인력 1만5000명을 채용하겠다고 밝혔다. 이처럼 막대한 지원의 초점은 사람, 즉 전문 인력 양성에 맞춰져 있다. 시스템 반도체 산업의 핵심 경쟁력인 전문 인력과 기술에 대해 집중적으로 살펴봤다.

시스템반도체란 무엇인가

‘비메모리 반도체인 시스템반도체는 논리 연산을 수행하는 로직 칩으로, 팹리스에서 설계해 파운드리에서 제조하며···’ 시스템반도체에 대한 설명을 읽다보면 슬슬 머리가 아파온다. 낯선 전문용어들 때문이다. 하지만 시스템반도체는 멀리 있는, 어려운 기술이 아니다. 여러분이 손에 쥔 스마트폰에도 50개 이상 들어있다. 시스템반도체가 무엇인지, 왜 중요한지, 앞으로 어떻게 발전할지 3가지 키워드로 정리했다.

키워드 ① 비메모리

미국 엔비디아에서 제작한 게임용 태블릿PC의 해부도. 작은 시스템반도체 칩(테그라 K1)이 태블릿의 두뇌 역할을 한다. 엔비디아

스마트폰과 컴퓨터를 비롯한 대다수의 전자기기에는 반도체 집적회로(IC·IntegratedCircuit)라고 하는 칩이 하나 이상 들어간다. 칩 안에는 수천, 수만 개의 트랜지스터, 저항, 커패시터 등과 전선이 복잡한 회로를 구성하고 있다.

반도체 칩은 역할에 따라 메모리 반도체와 비(非)메모리 반도체 크게 두 가지로 구분된다. 메모리 반도체는 잘 알려진 것처럼 데이터를 저장하고 기억하는 장치다. 전원을 껐을 때 데이터가 그대로 남아있는지 날아가 버리는지에 따라 D램(또는 S램), 플래시 메모리로 나뉜다.

시스템반도체는 메모리가 아닌 비메모리 반도체에 속한다. 시스템반도체는 데이터를 처리하는 역할을 한다. 그 종류는 8000여 종이나 된다. 가령 컴퓨터에 들어있는 중앙처리장치(CPU)나 스마트폰의 중앙처리장치인 애플리케이션 프로세서(AP)는 데이터를 연산하고 판단하는 처리를 한다(논리적인 연산 기능을 수행한다고 해서 해외에서는 시스템반도체 대신 ‘로직 칩(Logic Chip)’이라고 부른다). 그런가하면 모뎀은 데이터를 주고받으며 통신 기능을 하고, 카메라에 들어있는 이미지센서는 데이터를 수집하는 기능을 한다.

시스템반도체 산업은 팹리스(설계)와 파운드리(위탁생산)로 분리돼 있다. 사진은 전세계 파운드리 시장의 48%를 차지하고 있는 대반 TSMC에서 반도체를 생산하는 모습이다. TSMC 제공

시스템반도체는 제조 과정이 분업화돼 있다. 메모리 반도체는 삼성전자나 인텔 같은 종합반도체기업(IDM)이 설계, 가공, 조립, 마케팅 등을 총괄하는 반면, 시스템반도체는 설계전문기업인 팹리스(Fabless·반도체 생산시설인 ‘Fab’이 없다는 의미)에서 설계를 하면 생산전문기업인 파운드리에서 위탁 생산한다. 미국의 퀄컴, 엔비디아 등이 대표적인 팹리스 기업이고, 대만의 TSMC, 삼성전자가 파운드리에 집중하고 있다.

노예철 한국전자통신연구원 서울SW-SoC융합R&BD센터 실장은 “다양한 반도체 수요가 생겨나면서 전 세계적으로 아이디어 경쟁이 치열하다”며 “소자와 회로를 가장 효율적으로 배치하는 기술부터 시스템반도체를 응용하는 소프트웨어 개발까지 다양한 분야의 전문 인력, 전문 기업이 필요하다”고 말했다.

키워드 ② 인공지능

차량 또는 사물에 인공지능(AI) 기술을 구현하기 위해서는 딥러닝이 가능한 전용 시스템반도체를 개발해야 한다. 테슬라, 구글, 엔비디아 등 글로벌 기업들이 인공지능(AI) 반도체 개발에 뛰어들고 있다.

현재 시스템반도체 시장의 규모는 메모리 반도체 시장의 약 1.5배로, 2022년에는 300조 원 규모로 성장할 것으로 보인다. 가파른 성장세의 이유는 시스템반도체가 4차 산업혁명의 핵심인 인공지능(AI)을 실생활에 구현하기 위한 핵심 부품이기 때문이다. 사물인터넷(IoT), 자율주행자동차, 지능형 로봇도 마찬가지로 시스템반도체 없이는 구현할 수 없다.

인공지능 기술의 핵심은 학습과 추론이다. 두 가지 과정을 반복 실행하며 최적의 답을 찾아나간다. 기존의 인공지능 시스템은 대규모 연산 처리가 쉬운 데이터센터 서버에서 주로 이를 실행했다. 하지만 최근에는 드론, 자동차, 스마트폰 같은 디바이스 자체에서 인공지능 연산을 수행하도록 하는 추세다. 작고, 성능이 뛰어나며, 전력을 적게 쓰는 반도체 개발이 필수다.

대표적인 예로 화웨이는 지난해 듀얼 뉴럴프로세싱유닛(NPU) 기술이 적용된 모바일 AP ‘기린 980’을 개발해 인공지능에 특화된 스마트폰 ‘메이트 20’을 개발했다. 구글은 2017년 10월 ‘알파고 제로’에 단 4개의 TPU(인공지능 전용 반도체) 칩을 적용했다. 이세돌과 대전을 펼친 ‘알파고 리’에 비해 칩 개수는 12분의 1, 전력 소모는 10분의 1로 줄였다.

고성능 시스템반도체를 만드는 방식은 여러 가지다. 현재 가장 많이 쓰이는 방식은 그래픽처리장치(GPU)와 같은 ‘인공지능 가속기’를 넣어 설계하는 것이다. CPU로만 이뤄진 반도체는 대규모 데이터 처리 능력이 떨어진다. CPU가 중앙에서 모든 데이터를 순차적으로 처리하고 제어하기 때문에 연산하는 양이 많아질수록 CPU와 메모리 사이의 병목현상이 발생해 속도가 떨어지고 전력 소모가 크다.

그런데 GPU는 방대한 데이터를 동시에 처리할 수 있는 병렬 처리 구조다(본디 게임에서 3D그래픽을 처리하기 위해 개발됐다). 그래서 다양한 이미지를 통계 처리해 학습하는 딥러닝의 효율을 향상시킬 수 있다.

실제로 비주얼 컴퓨팅 기술 분야 기업인 엔비디아는 최근 CPU와 GPU가 통합된 ‘자비에(Xavier)’ 반도체를 개발하고 자율주행자동차에 적용할 계획이다. 자비에 칩에는 512개 코어로 구성된 GPU와 8개 코어로 구성된 CPU, 컴퓨터 비전 액셀러레이터(CVA) 등이 들어있다.

김선욱 엔비디아 기술마케팅 이사는 “미래에는 자동차가 스스로 주변 환경을 감시하고 위치를 파악하는 등 인공지능 기능이 더 중요해질 것”이라며 “고성능의 CPU와 GPU를 이용해 시스템의 성능을 계속 높여나가고 있다”고 밝혔다.

키워드 ③ 뉴로모픽

인간의 두뇌 구조를 모방한 뉴로모픽 반도체는 차세대 지능형 시스템반도체로 각광받고 있다. 이를 위해 전 세계 연구자들이 새로운 재료, 소자, 설계를 연구하고 있다.

시스템반도체는 향후 뉴로모픽 반도체(Neuromorphic Chips)로 진화할 전망이다. 뉴로모픽 반도체는 기존의 반도체 구조가 아닌 인간 뇌의 물리적 구조를 모방한 반도체다.

프로그램을 메모리에 저장한 후 순차적으로 읽어내 프로그램을 실행하는 기존 컴퓨터의 반도체 구조는 정보의 병목 현상, 무어의 법칙(반도체 집적회로의 메모리 용량과 속도가 1년 6개월마다 두 배 증가한다는 내용) 등 한계가 많았다.

뉴로모픽 반도체는 이를 돌파하기 위해 나왔다. 뇌신경망처럼 뉴런과 시냅스 구조로 반도체를 설계해, 하나의 반도체가 연산, 저장, 통신 기능을 한다.

대표적인 뉴로모픽 반도체는 IBM이 2014년 개발한 ‘트루노스(TrueNorth)’다. 트루노스는 54억 개 트랜지스터를 내장한 4096개의 반도체를 이용해 100만 개의 뉴런과 2억6000만 개의 시냅스(뉴런 접합부)로 얽힌 인간 두뇌를 모방했다. 트루노스는 기존 시스템보다 1만분의 1 수준으로 적은 전력(25~275㎽)으로 구동했다. 덕분에 그해 국제학술지 ‘사이언스’가 선정한 ‘올해의 10대 연구 성과’에 선정되기도 했지만, 사실 자가 학습능력은 없었다.

인텔은 2017년 학습 기능을 보완한 뉴로모픽 반도체 ‘로이히(Loihi)’를 개발했다. 로이히는 사람이 데이터를 입력하며 정답을 알려주는 지도학습 대신, 실시간으로 유입되는 정보를 받아들여 스스로 학습하는 기능을 갖췄다. 총 13만 개의 뉴런과 1억3000만 개 시냅스를 14나노미터(㎚·1㎚는 10억분의 1m) 선폭으로 제작했다. 지금까지 개발된 뉴로모픽 반도체 중 집적도가 가장 높다.

국내에서는 SK하이닉스가 2016년부터 미국 스탠퍼드대 연구팀과 함께 유기물질인 ‘강유전체(ferroelectrics)’를 이용해 인공신경망 반도체 소자를 개발하고 있다. 강유전체는 전기장을 가하지 않아도 양극과 음극의 분극이 일어나고, 전기장을 가하면 분극이 바뀐다. 전압에 따라 분극 상태를 부분적으로 조절할 수도 있다. 데이터를 0과 1 외에도 다양한 상태로 나타낼 수 있는 셈이다.

또 한국과학기술연구원(KIST)과 KAIST, 서울대, 포스텍, UNIST, 국민대, 어바인 캘리포니아대(UC어바인) 등 7개 기관이 2021년까지 총 120억 원을 투입해 자가 학습이 가능한 뉴로모픽 반도체 ‘네오(NeO)2C’를 개발 중이다.

노 실장은 “경쟁력이 있는 시스템반도체 기업을 육성하기 위해서는 기업과 대학, 연구소가 협력할 수 있도록 전략적인 지원이 필요하다”고 강조했다.

(원문: 여기를 클릭하세요~)